実験室用マイクロ波シンセサイザー。 スキーム、説明

§ 1.10 からわかるように、原理的には、マイクロ波を含む任意の周波数範囲でデジタル位相ロック ループを使用して DKSCH システムを構築することが可能です。 このようなシステムに関するよく知られた出版物は、デシメートル範囲 (たとえば、 、 ) にすぎませんが、その起源は 60 年代後半にまで遡ります。 SMV シリーズに関しては、この範囲のデジタル シンセサイザーについて説明した 1971 年の記事が 1 件だけ知られています。 最大 400 MHz の範囲のシンセサイザーはメーターの波長範囲に属し、メーターの限界よりわずかに大きい範囲をカバーするだけでなく、その構造原理からもその範囲に近いことに同意しましょう。

最も単純なデジタル シンセサイザーの動作周波数範囲の幅は DPCD の最大速度を超えることができないため、実際には最も単純な DLL システムはマイクロ波には適用できません。 DPKD の前に DPKD をオンにすると、システムの慣性が大きくなり、DPKD のノイズ特性が悪化することが上で述べられました。 実際、最新の DPCD の最大速度が約 50 MHz である場合、f 0 = 5 GHz (センチメートル範囲の中央) では、分周係数 c = 100 の DPCD が必要です。つまり、他の条件が等しい場合、帯域はこの例では、DPLLL リングの幅がこれより 2 桁狭くなります。

§ 1.10 で示したように、ヘテロダイン DFLL システム (図 1.12c) は、より大型ではありますが、最も単純なシステムに劣らない電気特性を備えています。 DPKD の速度によって制限されないため、マイクロ波シンセサイザーで使用できます。 ただし、このシステムの電子レンジでの使用には独自の特徴があります。 まず、マイクロ波での動作周波数範囲 P 0 = f 0 max - f 0 min の幅は、ほとんどの場合 DPKD の速度 f DP max を超えるため、ヘテロダインは 1 つの周波数ではなく、基準グリッドによって実行する必要があります。周波数 f q (k) (古い 10 年単位の DKSCH システムと同様)。 第二に、指定されたグリッドの離散性ステップ β k は、DPKD の安定分割範囲の幅 f DP max - f DP min、つまり実際には β k f DP max - f DP min を超えてはなりません。その場合、DPKD の前に次のようにします。 1 つまたは 2 つのトリガーの形式で DPKD をオンにする必要があります。 DPKD のこのような小さな分割係数 (c = 2 または c = 4) は、第一に、システムの電気的特性を著しく悪化させることはなく、第二に、業界がより高速に作用する DPKD を開発するにつれて、DFKD は最初に劣化します。単一のトリガー (c = 2) を使用すると、スキームから完全に除外できます。

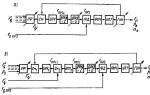

したがって、デジタル シンセサイザーの典型的なマイクロ波ブロック図は図のように表すことができます。 3.1a. このシステムの場合

(3.1) と (3.2) の結合解は次のようになります。

次に、(3.3) と (3.4) から DPKD の除算係数を求めます。

第 2 章では、基準周波数を選択するための基準 [形式 (2.44)] が定義され、シンセサイザーの出力で PLL リングによって制御されない副成分が存在しないことが保証されました。 これらの基準がどのように満たされるかを図の図で見てみましょう。 3.1a. なぜなら

次に、(3.6) を (3.1) に代入すると、次のようになります。

(2.44) から、次の条件を満たす必要があることがわかります。 ![]() 最後の式の極端な場合 (不等式を等号に置き換える)、これを考慮して (3.8) を (3.7) に代入すると、次のことがわかります。

最後の式の極端な場合 (不等式を等号に置き換える)、これを考慮して (3.8) を (3.7) に代入すると、次のことがわかります。

ただし、原則として、マイクロ波システムでは P 0 >> f DC max. したがって、DFCD 除算係数を十分に大きく選択するか、図のシステムの条件 (2.44) を選択する必要があります。 3.1a は特殊な場合にのみ満たされます。

しかし、ここでは同じ結論に達することができることが認められました。

システムパラメータに対する DFCD のマイナスの影響は、特に c が大きい場合に示されました。 近い将来、朝鮮民主主義人民共和国の業績が急激に向上することは期待できない。 したがって、システム図 3.1a は狭帯域シンセサイザーでのみ使用できます。

不等式 (2.44) の 1 つが満たされることは必須であると考えられるため、基準周波数 f" q " を上または下に転置する必要があります。シンセサイザーが受信機で動作する場合、シンセサイザーの動作範囲を超えます。この場合、明らかなように、条件 (2.44) をもう 1 つの不等式で補う必要があります。

特許 RU 2580068 の所有者:

本発明は無線工学に関するものであり、マイクロ波周波数範囲の送信および受信装置に使用することができる。 技術的な結果は、入力マイクロ波信号の周波数を調整する際の安定した動作を向上させることです。 マイクロ波周波数シンセサイザーには、マイクロ波電圧制御発振器 (VCO)、方向性結合器、マイクロ波ミキサー、入力マイクロ波信号源、可変分周係数を持つ第 1 分周器、周波数位相検出器、第 2 周波数が含まれています。可変分周係数を備えた分周器、基準信号源、フィルタ、ローパス、位相比較器、スタンバイマルチバイブレータ、2 つのダイオード、およびオペアンプ。 4 病気。

本発明は、無線工学、すなわち、マイクロ波の広域位相ロックループ(PLL)システムに含まれる、マイクロ波電圧制御発振器(VCO)の予備的、初期周波数設定を備えた広域マイクロ波周波数シンセサイザに関する。周波数シンセサイザーであり、マイクロ波周波数範囲のトランシーバー デバイスで使用できます。

アクティブ周波数合成システムが知られており、このシステムでは、合成された周波数の発振が、位相ロックループの形態のアクティブフィルタを使用してフィルタリングされる。 この場合、信号周波数は、たとえば低周波数範囲に分割することによって変換され、基準発振器の周波数と比較され、電圧制御マイクロ波発振器 (VCO) の自動調整電圧が計算されます。生成された。 アクティブ合成システムは、搬送波のスプリアススペクトル成分と位相ノイズをより高度に抑制します。 ただし、この回路では、VCO の分周比が高いため、シンセサイザー出力信号の低ノイズ レベルを達成することができません。

PLLループによる能動合成の原理を実装するマイクロ波周波数シンセサイザが知られており、これが提案された発明のプロトタイプとして選ばれた。 マイクロ波周波数シンセサイザーにはマイクロ波 VCO が含まれており、その出力は方向性結合器を介してマイクロ波周波数シンセサイザーの出力とマイクロ波ミキサーの 1 番目の入力に接続され、2 番目の入力はソースの出力に接続されます。周波数 f の入力マイクロ波信号のマイクロ波入力。マイクロ波ミキサーの出力は可変分周係数 n を持つ最初の分周器 (DF) の入力に接続され、その出力は周波数の最初の入力に接続されます。 - 位相検出器(FPD)、周波数位相検出器の 2 番目の入力は可変分周係数 m を持つ 2 番目の分周器の出力に接続され、その入力は基準周波数信号 f OP のソースに接続されます。周波数位相検出器の出力は、ローパス フィルター (LPF) を介してマイクロ波 VCO の入力に接続されます。 この場合、方向性結合器、ミキサー、第 1 分周器、PFD、ローパス フィルターが PLL ループを形成します。

既知のマイクロ波周波数シンセサイザは、ある周波数を有する入力マイクロ波信号として使用される場合に、第1の分周器の分周係数を低減することによって、周波数f MF を有するマイクロ波周波数シンセサイザの出力信号における低レベルの位相雑音を達成することを可能にする。 f 入力マイクロ波信号の位相ノイズが低い。 さらに、最初の分周器の分周比を下げると、PLL ループのゲインを増やすことができます。 このような回路では、入力マイクロ波信号の周波数 f in マイクロ波は f in マイクロ波 >f MF という条件から選択されるため、マイクロ波周波数シンセサイザーの PLL ループのゲインを一定の値に維持するには、次のようになります。 PLL ループ制御帯域を維持するには、マイクロ波 VCO の周波数同調スロープを変更することで、最初の分周器の分周係数の変化を補償する必要があります。

ただし、周波数ドリフト f VCO マイクロ波 VCO が 2 f IF (中間周波数 f IF = f 入力マイクロ波 -f VCO) を超える場合、このマイクロ波周波数シンセサイザーで位相同期エラーが発生し、機能の損失につながります。シンセサイザーの。

さらに、既知のマイクロ波周波数シンセサイザは、固定周波数f micrawave inputを有する入力マイクロ波信号がマイクロ波ミキサの第2の入力に供給される場合にのみ動作する。 マイクロ波の可変(調整可能な)周波数 f を持つ入力マイクロ波信号が 2 f IF 以上の帯域でマイクロ波ミキサーのこの入力に供給されると、マイクロ波周波数シンセサイザーでも位相同期違反が発生する可能性があります。

本発明の技術的目的は、低レベルの位相ノイズと、シンセサイザの出力信号の周波数f MF の同調時間が短い、広範囲のマイクロ波周波数シンセサイザを作成し、動作時に位相同期違反がないことを保証することである。入力マイクロ波信号 f 入力マイクロ波の周波数を、中間周波信号 f IF の 2 倍以上の帯域で変更 (調整) します (f IF = f 入力マイクロ波 -f VCO)。また、保存を保証します。マイクロ波 VCO 信号の周波数 f VCO が 2 f IF を超えて移動した場合の位相同期のずれ。

技術的な結果は、PLL ループ内の過渡プロセスによって引き起こされる位相同期の違反を防止し、マイクロ波入力信号の周波数 f input を調整するときを含む、動作中のマイクロ波周波数シンセサイザーの安定した動作を保証することです。

この技術的解決策の本質は、提案されているマイクロ波周波数シンセサイザに電圧制御マイクロ波発振器 (VCO) が含まれており、その出力が方向性結合器の入力に接続されており、その最初の出力がマイクロ波周波数の出力であるということです。方向性結合器の第2の出力はマイクロ波ミキサの第1の入力に接続され、マイクロ波ミキサの第2の入力は入力マイクロ波信号源の出力に接続され、マイクロ波ミキサの出力はシンセサイザに接続される。可変分周比を持つ第 1 分周器の入力。その出力は周波数位相検出器の第 1 入力に接続され、周波数位相検出器の第 2 入力は第 2 分周器の出力に接続されます。可変分周比の入力は基準信号源の出力に接続されており、周波数位相検出器とマイクロ波 VCO の間にローパス フィルターが接続されています。 マイクロ波周波数シンセサイザーにはさらに、位相比較器、スタンバイ マルチバイブレーター、2 つのダイオード、およびオペアンプが含まれています。 この場合、周波数位相検出器の第 1 出力と第 2 出力は、それぞれオペアンプの第 1 入力と第 2 入力に接続され、オペアンプの出力はマイクロ波 VCO の入力とローパスアンプに接続されます。フィルタはオペアンプの第 1 入力とその出力の間に接続され、位相比較器の第 1 入力は可変分周係数を持つ第 1 分周器の出力と周波数位相検出器の第 1 入力に接続され、第 2 の位相比較器の入力は可変分周係数を持つ 2 番目の分周器の出力と周波数位相検出器の 2 番目の入力に接続され、位相比較器の出力は待機中のマルチバイブレータの入力に接続されます。待機マルチバイブレータの出力は、第 1 ダイオードを介して周波数位相検出器の第 1 出力およびオペアンプの第 1 入力に接続され、スタンバイ マルチバイブレータの第 2 出力は、第 2 ダイオードを介して周波数位相検出器の第 2 出力に接続されます。 -位相検出器とオペアンプの2番目の入力に接続されます。 さらに、第 1 と第 2 のダイオードは互いに逆に接続され、マイクロ波 VCO、方向性結合器、マイクロ波ミキサー、第 1 の分周器、周波数位相検出器、オペアンプ、およびローパス フィルターがフェーズ ロック ループ (PLL) を形成します。 : T M - τ m >τ PLL、ここで、T M は待機中のマルチバイブレータの発振周期、τ PLL はフェーズ ロック ループで同期を確立する時間です。

位相比較器と、出力に 2 つの逆並列ダイオードを備えたスタンバイ マルチバイブレーターをマイクロ波周波数シンセサイザーの回路に組み込むことにより、マイクロ波 VCO の VCO 信号の周波数 f を事前に設定できるようになります。 PLL ループ内の位相同期の違反。これは、入力マイクロ波信号の周波数 f を切り替えるとき、またはマイクロ波 VCO 信号の周波数 f VCO を離れるときに発生します。たとえば、マイクロ波シンセサイザーをオンにするとき、位相同期の迅速な回復が保証されます。マイクロ波周波数シンセサイザーの安定性が向上します。 この場合、PLL ループが復元された後、スタンバイ マルチバイブレータはオフになり、PLL ループのその後の動作には影響しません。

フィードバック回路内のローパス フィルターを備えたオペアンプは、PLL ループの制御帯域幅を形成します。

待機中のマルチバイブレーターの最初のパルスの終わりと次のパルスの始まりの間の時間は、このマルチバイブレーターの RC 回路によって決定され、PLL ループで同期を確立する時間より大きくなければなりません。つまり、次の条件が満たされなければなりません。満たした:

TM -τ m >τ PLL。

本発明を図面によって説明する。

図では。 図 1 は、提案されたマイクロ波周波数シンセサイザーのブロック図を示しています。

1 - 周波数 f VCO (制御電圧 U UPR) のマイクロ波発生器 (VCO);

3 - 電子レンジミキサー;

4 - 周波数 f マイクロ波入力の入力マイクロ波信号のソース。

5 - 可変分周比 n を持つ最初の分周器。

6 - 周波数位相検出器(出力電圧 U PFD)。

7 - 可変分周比 m を持つ 2 番目の分周器。

8 - 周波数 f OP の基準信号源。

9 - オペアンプ。

10 - ローパスフィルター。

11 - 位相比較器(出力電圧U FC)。

12 - スタンバイ マルチバイブレータ (直接出力電圧 U m1 および逆出力電圧)

13 - 最初のダイオード。

14 - 2番目のダイオード。

f IF =f マイクロ波入力 -f VCO - 中間周波信号;

f MF - マイクロ波周波数シンセサイザーの出力信号。

図では。 図 2 は、提案されたマイクロ波周波数シンセサイザの一部である待機マルチバイブレータの入力 U FC と出力電圧 U m1 および U m2 のタイミング図を示しています。

T M −待機マルチバイブレータ12の発振周期。

τ m −待機中のマルチバイブレータ12のパルス持続時間。

τ PLL は、フェーズ ロック ループで同期を確立する時間です。

図では。 図 3 は、提案されたマイクロ波周波数シンセサイザの固定周波数 f 入力マイクロ波信号に対する周波数 f MF =f VCO の出力マイクロ波信号の同調帯域幅を示しています。

図では。 図 4 は、提案されたマイクロ波周波数シンセサイザの調整可能な周波数 f 入力マイクロ波入力信号に対する周波数 f MF =f VCO の出力マイクロ波信号の調整帯域幅を示しています。

提案されたマイクロ波周波数シンセサイザのブロック図を図に示します。 このマイクロ波電圧制御発生器(VCO)1は、その出力が方向性結合器2の入力に接続されており、その一方の出力はマイクロ波周波数シンセサイザの出力であり、もう一方の出力は方向性結合器である。図2のマイクロ波ミキサ3は、マイクロ波ミキサ3の第1の入力に接続され、その第2の入力は、周波数f マイクロ波入力 の入力マイクロ波信号4の出力源に接続されている。 マイクロ波ミキサ3の出力は、可変分周係数nを有する第1の分周器5の入力に接続され、その出力は、周波数位相検出器6の第1の入力に接続される。位相検出器6は可変分周係数mを有する第2分周器7の出力に接続され、その入力は周波数f OP を有する基準信号源8の出力に接続される。 周波数位相検出器6の2つの出力は演算増幅器9の2つの入力に接続され、演算増幅器9の出力はマイクロ波VCO発生器1の入力に接続され、ローパスフィルタ10が周波数位相検出器6の第1の入力間に接続される。回路11に追加的に導入された位相比較器の第1の入力は、第1の分周器5の出力および周波数位相検出器6の第1の入力、位相の第2の入力に接続されている。比較器11は、第2の分周器7の出力および周波数位相検出器6の第2の入力に接続されている。位相比較器11の出力は待機マルチバイブレータ12の入力に接続されており、その出力は待機マルチバイブレータ12を介して導かれる。第1のダイオード13は周波数位相検出器の第1の出力および演算増幅器9の第1の入力に接続され、スタンバイマルチバイブレータ12の反転出力は第2のダイオード14を介して周波数位相検出器の第2の出力に接続される。図6に示すように、演算増幅器9の第2の入力には、第1および第2のダイオードが互いに逆向きに接続されている。 この回路では、マイクロ波VCO1、方向性結合器2、マイクロ波混合器3、第1の分周器5、周波数位相検出器6、第2の分周器7、オペアンプ9、ローパスフィルタ10によりPLLループが形成されている。

提案されたマイクロ波周波数シンセサイザは次のように動作します。 カプラ2を介した周波数f VCO のマイクロ波VCO1の出力信号と、周波数f 入力マイクロ波 を有する入力マイクロ波信号源4の出力マイクロ波信号は、マイクロ波ミキサ3に供給され、その出力で中間周波数f IF の信号が出力される。が選択され、第 1 分周器 5 の入力に供給され、係数 n で分周した後、第 1 分周器 5 の出力からの信号が周波数位相検出器 6 の第 1 入力に供給されます。基準信号源8の出力からの周波数信号f OP は、第2の分周器7の入力に供給され、そこで周波数が係数mで分周される。 第2の分周器7の出力からの信号は周波数位相検出器(FPD)6の第2の入力に供給され、そこで第1の分周器5の出力から受け取った信号と比較され、制御が行われる。電圧U FPD は周波数位相検出器6の2つの出力で生成され、その大きさと符号は比較される信号の周波数と位相の差に比例する。 この制御電圧U PFD は、オペアンプ9と、オペアンプ9のフィードバック回路に含まれるローパスフィルタ10を介して、制御電圧U Ctrl としてマイクロ波VCO1の制御入力に供給され、マイクロ波VCO1の制御入力に供給される。マイクロ波 VCO 1 の周波数を継続的に調整し、PLL ループ内の位相モード同期に影響を与えます。

PLL ループで周波数位相同期を実行するための条件は、周波数位相検出器の入力に供給される信号の周波数と位相が等しいことです。つまり、f OP /m=f IF /n、φ OP = φIF、

ここで、f IF = f 入力マイクロ波 -f VCO、

mは、周波数f OP の基準信号の周波数の除算係数です。

nは中間周波信号f IF の分周係数です。

φ OP - 周波数 f OP の基準信号の位相。

φ IF - 中間周波信号 f IF の位相。

入力マイクロ波信号 f in マイクロ波の周波数が中間周波信号 f IF の 2 倍以上の帯域で調整される場合 (f IF = f in マイクロ波 -f VCO)、およびマイクロ波信号 f VCO f VCO が 2 f IF を超えて移動すると、提案された発明における入力マイクロ波信号 f 入力マイクロ波は、マイクロ波周波数シンセサイザーの PLL ループ、つまり位相比較器 11、待機マルチバイブレーター 12 を通過します。およびバックツーバック ダイオード 13、14。

PLLループに位相同期がある場合、位相比較器11の出力から待機マルチバイブレータ12への制御信号が受信され、待機マルチバイブレータ12がオフになる、すなわち、位相比較器11の出力電圧U FC がオフになる。 (たとえば、トランジスタ - トランジスタ ロジック TTL のレベル) 論理ユニットの形式で。 このとき、待機中のマルチバイブレータ12は、直接出力および反転出力にそれぞれ電圧U M1 、U M2 を有するパルス出力信号を生成せず、PLLループの動作に影響を与えない。 待機マルチバイブレータ12の直接および逆出力では、定電圧U M1 およびU M2 が逆位相に設定され、論理0および論理1に対応する。 待機マルチバイブレータ12の入力電圧U FC と出力電圧U M1 およびU M2 のタイミング図を図2に示す。 2

PLLループ内の周波数および位相の同期が乱されると、位相比較器11の出力からの論理0の形のU FC 信号がスタンバイマルチバイブレータ12をトリガし、直接出力および反転出力で次のような出力パルス信号を生成する。電圧U M1 (論理ユニットに対応)およびU M2 (論理ゼロに対応)は、それぞれダイオード13、14を介して演算増幅器9の第1および第2の入力に到達する。待機マルチバイブレータのパルスの動作中。 12、すなわち、待機マルチバイブレータ12のパルスの持続時間τ m の間、PFD6の入力の位相に応じて、出力オペアンプ9は、周波数に対する制御電圧の最大値または最小値を設定する。この場合、周波数位相同期の条件が違反され(f OP /m=f IF /n、φ OP =φ IF )、周波数位相検出器6が制御電圧を生成する。 U PFD。PLL ループでの同期の回復 (つまり、同期プロセスの開始) を保証します。 PLLループにおいて周波数位相同期が回復すると、位相比較器11はスタンバイマルチバイブレータ12をオフにする(その出力では、論理0および論理1に対応する定電圧が再び逆位相に設定される)。 PLLループ内で周波数位相同期が繰り返し違反された場合、またはPLLループが誤動作した場合、位相比較器11は待機中のマルチバイブレータ12を再び起動し、同期を回復するプロセス全体が繰り返される。

場合によっては、PLL ループの動作では、周波数位相同期の違反を除いて、PLL ループ内のマイクロ波 VCO の周波数を調整する過渡プロセスを低い方 (f VCO min) から開始する必要があります。 ) マイクロ波 VCO の動作範囲の上限 (f VCO max) エッジから f VCO = f MF となる周波数捕捉点まで、つまりマイクロ波 VCO 1 の制御入力に供給される初期電圧レベル (過渡状態)周波数キャプチャに先行するモード)、常に最小値または最大値と等しかった。 これは、マイクロ波入力信号のマイクロ波周波数 f に対するマイクロ波 VCO 出力信号の VCO 周波数 f の位置によって決まります。 この場合、マイクロ波周波数シンセサイザには 2 つの主な動作モードが考えられ、PLL ループの同期が中断される可能性があります。

図に示す、マイクロ波周波数シンセサイザーの最初の動作モードを考えてみましょう。 3. マイクロ波入力信号の周波数 f が固定されており、(プロトタイプと同様) f MF を超えており、マイクロ波 VCO 1 の同調帯域 (Δf VCO) が十分に大きい、たとえば値を大幅に超えていると仮定します。 2 f IFの。 この場合、周波数捕捉に先立つ過渡プロセス中に、マイクロ波ミキサ 3 の出力からのミラー周波数信号が周波数位相検出器 6 に到達する可能性があります (同期失敗の時点で、f VCO = f 1 MF、ここで f 1 MF = f 入力マイクロ波 +f IF)、これは PLL ループでの同期の失敗、マイクロ波 VCO の周波数 f VCO 信号の周波数 f VCO max に対応する最上位位置への遷移につながります。その結果、マイクロ波周波数シンセサイザーの動作が失敗します。 プロトタイプとして選ばれたマイクロ波周波数シンセサイザーの回路には、この状況を解決する可能性はありません。 提案されたマイクロ波周波数シンセサイザでは、この問題は次のように解決される。

周波数位相同期モード(f OP /m=f IF /n、φ OP =φ IF )の位相比較器11は、論理ユニット(論理「1」)に対応する信号U FC をその出力に生成する。 位相比較器11のこの出力は、論理ゼロ(論理「0」)に対応する信号によってトリガされる待機マルチバイブレータ12の入力に接続される。 ログレベルと等しい入力信号の場合。 「0」の場合、最初のダイオード13および第2のダイオード14は閉じられ、スタンバイマルチバイブレータ12はPLLループの動作に影響を及ぼさない。 位相同期モードが違反された場合、ログに対応する信号が位相比較器11の出力に現れる。 「0」。 これは、マイクロ波周波数シンセサイザがオンになっているとき、または基準信号の周波数 f が調整されているときに発生する可能性があります。 ログに対応する信号。 位相比較器11の出力からの「0」はスタンバイマルチバイブレータ12をトリガし、その直接および反転出力において、パルス持続時間τ m の間、電圧レベルはそれぞれ対数「1」および対数に等しいように見える。 「0」(すなわち、前の状態の逆)、したがって、最初のダイオード13および第2のダイオード14が開き、差動電圧がオペアンプ9の第1および第2の入力に供給され、初期(最小)の状態が現れる。マイクロ波VCO1の周波数制御入力にそれぞれ供給される演算増幅器9の出力における制御電圧は、マイクロ波VCOの周波数値f VCO =f VCO minを設定する。 待機中のマルチバイブレータ12のパルスの終了後、値T M -τ m に等しい休止期間があり、ここでT M は待機中のマルチバイブレータ12のパルス繰り返し周期である。この休止中に、PLLループは周波数f VCO を調整する。最小値 f VCO min から、周波数位相同期が発生する周波数 までのマイクロ波 VCO 信号の変化 (図 3 の周波数ロック点)。 マイクロ波 VCO 信号の周波数 f VCO が、f VCO =f MF (f MF =f 入力マイクロ波 -f IF) となる値に調整され、f VCO ≤ f 入力マイクロ波の条件に従います (規定に従って)。 PFD 6) の位相調整により、f OP /m = f IF /n となる周波数位相同期モードが確立されます。 位相比較器11の出力には、対数レベルに対応する信号が現れる。 「1」、マルチバイブレータ12をスタンバイ状態に移行する。 何らかの理由で同期プロセスが発生しない場合は、PLL ループで同期を確立する前述のサイクルが繰り返されます。 この場合、周波数捕捉に必要な条件は、待機マルチバイブレータ12のパルス繰り返し周期が条件T M -τm>τ PLLループを満たさなければならないことである。

T M - 待機中のマルチバイブレータのパルス繰り返し周期、

τ m - 待機中のマルチバイブレーターのパルス持続時間、

τ PLL ループ - PLL ループで同期を確立する時間。

図に示す、マイクロ波周波数シンセサイザーの 2 番目の動作モードを考えてみましょう。 4.

マイクロ波周波数シンセサイザーの初期瞬間に、周波数位相同期の条件が満たされ、f 入力マイクロ波 = f 入力マイクロ波 1 であると仮定します。 この場合、マイクロ波周波数シンセサイザの出力信号の周波数は、f MF =f MF・1 =f入力マイクロ波1 -f IF となる。 次に、マイクロ波入力信号の周波数 f は、入力マイクロ波信号のマイクロ波同調の帯域 Δf 内で (図 4 に示すように)、マイクロ波 1 の値 f からマイクロ波 2 の値 f (この場合、周波数) に急速に調整されます。マイクロ波における入力マイクロ波信号の同調帯域 Δf は 2 f IF より大きく、f IF =f 入力マイクロ波 -f VCO の周波数調整 f 入力マイクロ波と同時に、f VCO マイクロ波 VCO の周波数調整は値 f MF1 から発生します。ただし、PLL ループの慣性により、入力マイクロ波信号 (t AC マイクロ波入力) の周波数同調時間は、常に PLL ループ (τ PLL ループ) の同期確立時間よりも小さくなります。つまり、t AC マイクロ波入力 ≤τ PLL ループです。

PLL ループの慣性の結果、マイクロ波 VCO の周波数を調整するときに、同期が中断される状況も発生します。 例えば、図2に示すように、 図4は、VCOの周波数fを初期値f MF1 (マイクロ波VCOの周波数同調範囲の上部)から次に低い周波数値f MF2 まで調整する場合を示す。 マイクロ波ミキサーでは、ミラー中間周波信号が f VCO = f 1 MF2 = fin マイクロ波 2 + f IF の点で形成されます。 この場合 (PFD 6 の所定の位相)、条件 f VCO ≤f マイクロ波入力は満たされません。つまり、周波数が PLL ループによって捕捉されず、PLL ループとの周波数位相同期の違反が発生します。周波数 f VCO を上限値 f VCO まで「ドラッグ」する マイクロ波 VCO の最大周波数同調範囲。 提案される発明のPLLループにおける周波数位相同期を回復するには、マイクロ波周波数シンセサイザの第1の動作モードで説明した同期確立サイクルを実行する必要がある。 プロトタイプとして選ばれたマイクロ波周波数シンセサイザーの回路は、入力マイクロ波信号の周波数を迅速に変更する機能を備えていないため、このような回路では入力マイクロ波の周波数を調整する際に安定した位相同期を実現できません。信号。

本発明のプロトタイプとして選ばれた周知のマイクロ波周波数シンセサイザにおけるPLLシステムの不安定な動作の上述のモードは、実験的にテストされ、確認された。

提案された発明に基づいて、マイクロ波周波数シンセサイザーのサンプルが開発され、実験的にテストされました。これにより、マイクロ波周波数シンセサイザーのさまざまな動作モードで周波数位相同期の高速回復時間が100μs未満で安定した動作が確認されました。

情報源

1. マナセビッチ V. 周波数シンセサイザー。 理論とデザイン。 - M.: コミュニケーション、1979 年

2. リシコフ A.V.、ポポフ V.N. 無線通信技術における周波数シンセサイザー。 - M.: ラジオと通信、1991 年、p. 110-113。

電圧制御マイクロ波発振器 (VCO) を含むマイクロ波周波数シンセサイザー。その出力は方向性結合器の入力に接続され、その最初の出力はマイクロ波周波数シンセサイザーの出力であり、方向性結合器の 2 番目の出力は方向性結合器の入力に接続されています。カプラーはマイクロ波ミキサーの第 1 入力に接続され、マイクロ波ミキサーの第 2 入力は入力マイクロ波信号の出力源に接続され、マイクロ波ミキサーの出力は可変周波数を備えた第 1 分周器の入力に接続されます。分周比。その出力は周波数位相検出器の第 1 入力に接続され、周波数位相検出器の第 2 入力は可変分周比を持つ第 2 分周器の出力に接続され、その入力は基準信号源の出力に接続され、周波数位相検出器とマイクロ波 VCO の間にローパス フィルターが含まれます。マイクロ波周波数シンセサイザーにはさらに位相比較器、待機マルチバイブレーター、2 つのダイオード、および 1 つのダイオードが含まれることを特徴とします。周波数位相検出器の第 1 および第 2 の出力がそれぞれオペアンプの第 1 および第 2 の入力に接続されたオペアンプ。オペアンプの出力はマイクロ波 VCO の入力に接続され、ローパス フィルタはオペアンプの第 1 入力とその出力の間に接続され、位相比較器の第 1 入力は可変分周係数を持つ第 1 分周器の出力と第 1 入力周波数位相検出器に接続され、位相比較器の第 2 入力は比較器は可変分周係数を持つ 2 番目の分周器の出力と周波数位相検出器の 2 番目の入力に接続され、位相比較器の出力は待機マルチバイブレータの入力に接続され、待機マルチバイブレータの最初の出力に接続されます。マルチバイブレータは、第 1 ダイオードを介して周波数位相検出器位相検出器の第 1 出力に接続され、オペアンプの第 1 入力に接続され、待機マルチバイブレータの第 2 出力は、第 2 ダイオードを介して周波数位相検出器の第 2 出力に接続されます。位相検出器とオペアンプの 2 番目の入力、および 1 番目と 2 番目のダイオードが互いに逆に接続され、マイクロ波 VCO、方向性結合器、マイクロ波ミキサ、最初の分周器、周波数位相検出器、オペアンプおよびローパス フィルターは、次の条件の下でフェーズ ロック ループ (PLL) を形成します: T M -τ m >τ PLL、ここで、T M は待機中のマルチバイブレーターの発振周期、τ m は待機中のマルチバイブレーターの持続時間パルス、τ PLL は、フェーズ ロック ループで同期を確立する時間です。

類似の特許:

本発明は通信技術に関する。 技術的な成果は、同期システムの主要パラメータの包括的な改善で構成されます。つまり、ノイズ耐性の向上、システムのフィルタリング特性の改善、取得帯域の拡大、同期動作モードの維持、同期動作に入るまでの時間の短縮です。モードでは、静的位相誤差がゼロであることを保証し、入力信号の振幅の変化や変動、または位相検出器の伝達係数の変化が存在する場合でもデバイスの正しい動作を保証します。

本発明は、無線信号の周波数選択およびフィルタリングに関する。 技術的な成果は、無線信号選択デバイスを干渉条件に確実に適応させ、エネルギー消費を制御できるようにすることにあります。

スイッチング周波数低減パスを備えた周波数シンセサイザは無線工学に関連しており、ノイズ耐性が向上した受信デバイスや、動作周波数を迅速に調整するトランシーバ デバイスにおいて、均一なステップで安定した周波数のグリッドを形成するために使用できます。

提案された方法は、通信技術と、制御発振器(CG)を含む同期ユニット(BS)の動作モードに関連し、より正確には、ホールドモードでBS CGの非常に安定した出力信号を生成する方法に関する。

本発明は、電子機器、すなわち、フラクショナルノイズ補償を備えたパルス位相ロックループ(PLL)に基づく周波数グリッドシンセサイザ(GSS)に関するものであり、補償電流の振幅変調またはパルス幅変調に基づくスキームを使用する場合に使用することができる。

本発明は、無線工学および自動化の分野に関し、改善された安定化特性を備えた連続ガスレーザーからの放射の周波数を自動的に調整するシステムに関し、特に周波数の「バイオレットシフト」を測定するために宇宙技術で使用することができる。地球の重力場におけるレーザー放射の影響。

本発明は、電子コンピュータ技術および無線工学に関する。 技術的な結果は、速度が向上し、複数周波数の周波数変調信号を生成する能力が向上することです。 周波数変調信号のデジタル計算シンセサイザーには、基準発生器、整形および遅延ユニット、3 つのメモリ レジスタ、4 つのデジタル ドライブ、可変分周比の分周器、2 つの関数コンバーター code x - sin x、2 つの逆フィルター sin が含まれています。 x/x、整流子、2 つのデジタル - アナログ コンバーター。 FM DAC 信号のデジタル入力は、第 1、第 2、および第 3 のメモリ レジスタの入力であり、そのアナログ出力は第 1 および第 2 の DAC の出力です。 2 病気。

本発明は、無線工学の分野に関する。 技術的な結果は、符号付き論理位相弁別器の弁別特性の対称形状を非対称のものに変更し、弁別特性の正または負の符号の面積を増加させることによって捕捉帯域を拡大することです。対応する符号の初期周波数離調に対する対応する片側捕捉帯域が増加します。 前述の弁別器を使用してフェーズロックループシステムのキャプチャ帯域幅を増加する方法は、制御された発電機によって生成された入力発振と出力発振の間の差の符号を決定し、その符号に対応する符号を持つ制御電圧を生成することを特徴としています。位相差は、制御された発電機の周波数を制御する単一の信号に結合されます。 2n.p. ちと、7人病気です。

フェーズロックループ方式により、ノイズのある単相ソース信号からの同期が可能です。 技術的な成果は、実際の同期速度を同期周波数の信号の 1 または 2 周期に改善し、同期位相と周波数で生成された信号の干渉をフィルタリングすることにあります。 このシステムには、1 次位相フィルタリング、2 次バンドストップ フィルタ、1 次低周波フィルタリング、積分ブロック、乗算ブロック、デジタル フィルタ係数を計算するブロック、および 4 象限逆正接のブロックが含まれています。 。 マイクロプロセッサ手段を用いた方法の物理的実装に個別の方法を使用することにより、許容可能な精度および計算リソースを備えた非線形関数の比較演算および計算が可能になる。 フィルターは可変係数を使用して実装され、1 次と 2 次があります。 周波数の変化に対する位相フィルターの感度が比較的低いため、元の信号から基準位相を迅速に抽出することができます。 積分係数に対するフィードバックを備えた離散積分器を使用することにより、同期周波数信号が迅速に定常状態に達することができます。 可変係数を備えた離散フィルターを使用し、境界値による位相遷移を考慮することにより、元の信号の基本高調波の位相に対してシフトさせることなく同期位相を効果的にフィルター処理することが可能になります。 この方法を使用すると、単相および多相システムの高調波成分と多相システムの対称成分に基づいた制御システムを構築できます。 この方法の主な用途はコンバータ機器の制御ですが、通信における高速同期や、基本周波数への同調や基準位相の分離などの高性能要件を必要とするその他の用途にも使用できます。 1 病気。

本発明は、無線工学の分野に関し、小さなステップでの周波数調整が必要とされる測定技術だけでなく、チャネル数が増加した通信システムの組織化にも使用することができる。 本発明の基礎は、小さな周波数グリッドステップ、低レベルの位相ノイズ、および短い周波数同調時間でマイクロ波発振を得るという課題である。 このため、間接型シンセサイザーの位相検出器の比較周波数を設定する基準発振器の周波数は超短波帯で選択されます。 この場合、非常に安定した基準発振器の周波数が最初に一定の小さな量だけシフトされ、周波数グリッドの小さなステップが設定されます。 この目的のために、基準発振器の信号が直交変調器の無線周波数入力に供給され、同じ周波数と振幅で 90 度の位相シフトを持つ低周波直交信号によって変調されます。 そして、比較周波数は、これらの低周波信号の周波数の値だけ基準発振器の周波数と異なります。 直交変調器の出力からの周波数変換された信号は、周波数位相検出器の最初の入力に供給されます。 電圧制御マイクロ波発生器の周波数は、可変係数を備えた分周器によって分周され、周波数位相検出器の 2 番目の入力に供給されます。 ローパス フィルターを使用して、AC 基準成分が抑制され、DC 信号が電圧制御マイクロ波発振器の入力に供給されます。 この方法では、シンセサイザのチューニング時間を増加させることなく、位相ノイズのレベルを増加させることなく、基準発振器周波数の安定性によって決定されるシンセサイザ周波数の安定性を維持しながら、数キロヘルツのステップでマイクロ波発振を形成することができます。たとえば、10-7-10-8 に達します。

本発明は無線電子機器に関し、特に位相ロックループ(PLL)に基づく周波数シンセサイザに関する。 技術的な成果は、出力信号のスペクトル内の位相ノイズとスプリアス ディスクリート成分のレベルを低減することであり、これにより、高周波数分解能と広い同調帯域を維持しながら、出力信号の品質が向上します。 周波数シンセサイザーには、直列接続された入力信号周波数逓倍器、固定分周係数を持つ分周器、第 1 の直接デジタル合成マイクロ回路、位相周波数検出器、第 1 のローパス フィルター、電圧制御発生器、負帰還が含まれています。直列接続されたミキサーを含む回路。入力の 1 つは電圧制御発電機の出力に接続され、2 番目の入力は入力信号周波数逓倍器の出力に接続されます。2 番目のローパス フィルターと 2 番目のローパス フィルターが含まれます。出力が位相周波数検出器の入力に接続される直接デジタル合成マイクロ回路と、出力が第1および第2の直接デジタル合成チップの入力に接続される制御装置。 本発明は、出力信号のスペクトルにおける位相ノイズおよび離散成分のレベルを低減し、その結果、高周波数分解能および広い同調帯域を維持しながら出力信号の品質を向上させる。 1 病気。

本発明は無線工学に関する。 本発明の技術的成果は、速度が向上し、周期がクロック周期の倍数である任意のデューティサイクルの基準信号を扱う能力と、エッジに沿ってクロック周波数を調整する能力が向上することである。受信したデータの。 周波数調整方法。パルスの継続中に、位相検出器 (PD) の出力で正と負の極性の信号が生成され、それらが加算され、フィルタリングされ、その結果得られる信号が発生器の周波数を制御します。 、最初の出力のパルス フロントは基準信号のエッジに沿っており、クロックのスイッチングではそのカットオフに沿っています。 基準信号のエッジがクロック サイクルのエッジよりも後に現れる場合、クロック休止期間中に PD の 2 番目の出力でも信号が生成されます。 FD には 3 つの 2-I 要素、3 つの D フリップフロップ、および 3 つの信号を接続するための論理回路が含まれています。 2n. そして7の給料 なんと、11歳の病気です。

本発明はレーダーおよびソナーに関する。 技術的な結果は、奇数長の P3 コードのサイド ローブを抑制することです。 この目的のために、多相 P3 コードのパルス圧縮中にサイド ローブを抑制するデバイスには、入力に接続された奇数長 N の P3 コード用の修正 Woo フィルターと、直列接続されたコード コンバーターから複素数に変換するデジタル補正信号発生器が含まれています。共役コードと、(N+2) 個の係数 -1.1、0、…0、-1.1 を持つ次数 FIR フィルター N+1 の有限インパルス応答を持つデジタル フィルター、最初の入力に接続された加算器の出力、遅延1 つのコード要素の期間のラインと 2 入力減算器。Woo フィルターの出力は入力遅延線と減算器の最初の入力に接続され、出力は加算器の 2 番目の入力に接続されます。減算器の 2 番目の入力は遅延線の出力に接続され、修正フィルター Woo の最初のインパルス応答係数は 1 - exp(iπ/N) に等しくなります。ここで、 (N+2) 次元ベクトルデジタル補正信号整形器のフィルター係数は、それぞれ -1.1、0.0、…0、-1.1 に等しくなります。 2 病気。

提案されたデバイスは、多相コードのパルス圧縮を備えたレーダーおよびソナー システムに関連しています。 技術的な結果は、信号圧縮の品質を向上させることであり、圧縮プロセス中に発生するサイドローブが抑制され、タイムシフト (サンプル) のすべての値に対して、長さ N の多相コードの数が確実に増加します。 2 ±N。最初と最後の同じ数を連続して削除することによって形成された対称的に切り捨てられたコードの使用により、サイド ローブの相対レベルは -20 logN -6 ~ -20 logN -8 dB の範囲になります。より長いコードのシンボル。 この場合、-6 dB レベルでのメインローブの幅は 2τ、PSL レベルでは 3÷4τ の範囲になり、デバイス出力での信号/ノイズ損失は -1.7 dB になります。 長さ N の対称的に切り詰められた多相コードのパルス圧縮中にサイド ローブを抑制するデバイスには、入力に接続された次数 N-1 の FIR を備えた最初のデジタル フィルターと、複素数に直列接続されたコード コンバーターで構成されるデジタル補正信号発生器が含まれています。共役コードと有限インパルス応答次数 N+1 の 2 番目のデジタル フィルター。その出力は加算器の 1 番目の入力に接続され、最初のデジタル フィルターの出力は 1 秒間遅延線に接続されます。コード要素と減算器の第 1 入力に接続され、減算器の第 2 入力は遅延線の出力に接続され、出力は加算器の第 2 入力に接続されます。 3n.p. ちと、病気は4人。

このグループの発明はストレージデバイスに関するものであり、非調整アーキテクチャでストレージデバイスに書き込むタイミングを制御するために使用することができる。 技術的な結果は、実際のクロック信号配信ネットワークの遅延の変化を補償することです。 このデバイスには、受信回路とリング発振回路が含まれています。 受信回路には、データ パスとクロック分配ネットワークが非調整構成で含まれています。 リング発振回路には、実際のクロック分配ネットワークと一致するクロック分配ネットワークのレプリカが含まれています。 3n. そして17の給料 ちと、10人病気です。

タイムスケールジェネレータとは、周波数、位相シフト、およびタイムスケールによって信号を同期させるデバイスを指します。 技術的な結果は、タイムスケール同期の精度を高めることです。 タイム スケール ジェネレーターには、タイム スケール受信ブロック、内部量子シーケンス ジェネレーター、分周器、タイム スケール送信ブロック、ガード インターバル形成器、タイム セレクター、切り替え可能な遅延ラインのブロック、コンパレーター ブロック、および線形可変電圧発生器。 5 病気、1 タブ。

本発明は無線工学に関するものであり、マイクロ波周波数範囲の送信および受信装置に使用することができる。 技術的な結果は、入力マイクロ波信号の周波数を調整する際の安定した動作を向上させることです。 マイクロ波周波数シンセサイザには、電圧制御マイクロ波発生器、方向性結合器、マイクロ波ミキサー、入力マイクロ波信号源、可変分周係数を持つ第 1 分周器、周波数位相検出器、周波数位相検出器、第 2 分周器が含まれています。可変除算係数、基準信号源、ローパス フィルター、位相比較器、待機マルチバイブレーター、2 つのダイオード、およびオペアンプ。 4 病気。

著者: Alexander Chenakin (フェーズ マトリックス); 英語からの翻訳 ピバク A.V. 博士号発行日: 2007/05/01

周波数合成: 現在のソリューションと新しいトレンド

主な特徴

周波数シンセサイザーは、ほぼすべての通信、測定、制御システムの重要な要素です。 以下は、新世代のマイクロ波周波数シンセサイザーを設計するための主な要件です。

周波数範囲と分解能 。 多くのアプリケーションでは、固定信号または比較的狭帯域 (10 ~ 20%) の信号で十分な場合があります。 ただし、最新のデジタル ブロードバンド システムでは、数オクターブに及ぶはるかに広い周波数カバレッジが必要です。 広い周波数帯域幅と高分解能 (1 Hz 以下) は、実験室用周波数発生器やスペクトラム アナライザなどの測定機器にとって不可欠な要件です。多くのアプリケーションで使用できる汎用の広帯域ソリューションを開発することが適切と思われます。

出力電力。 必要な出力電力レベルは、特定のアプリケーションに応じて大きく異なります。 一般的なシナリオは、さまざまな周波数変換システムでミキサーの基準ソースとしてシンセサイザーを使用することです。 通常、10 ~ 17 dBm が許容可能なレベルですが、一部の回路ではより高い電力が必要です。

非高調波歪み。 非調和スペクトル成分 ( スパーズ) – 個別の離散周波数でシンセサイザーによって作成される不要な周波数積。 これらのコンポーネントの位置とレベルは、特定のシンセサイザーの構造アーキテクチャと周波数計画によって決まります。 マイクロ波通信システムでは、非高調波歪みにより、受信デバイスが受信信号を分離してさらに処理する能力が制限される可能性があります。 したがって、シンセサイザーの非調和スペクトル成分のレベルは最小限に抑えられ、原則として主信号のレベルに対して -60 dBn を超えませんが、場合によっては -80 dBn 以下に下げる必要があります。 。 これには周波数シンセサイザの設計にある程度の努力が必要であり、通常は他のパラメータ、特に位相ノイズのレベル、周波数分解能、チューニング速度との間で妥協する必要があります。

位相雑音と安定性 - 受信システムの感度を最終的に制限する主要なパラメータの 1 つ。 シンセサイザーの安定性と位相ノイズは基準信号 ( 参照)、およびシンセサイザーの特定のアーキテクチャ。 フェーズ ロック ループ (PLL) の使用に基づくシンセサイザーは、使用される調整可能な発振器にも依存します。そのノイズは、基本周波数から大きくオフセットされた基準信号の実効ノイズよりも低くなります。 良い例は YIG ジェネレーター ( YIG発振器)、そのノイズ レベルは、2 ~ 10 GHz 以上の周波数範囲で -120 ~ -130 dBc/Hz (100 kHz の離調あり) に達する可能性があります。

調整速度 シンセサイザーをある周波数から別の周波数にどれだけ速く調整できるかを決定します。 調整に必要な時間は、通常は信号処理に使用できないため、重要なパラメーターです。 新世代の通信システムでは、実効スループットを向上させるために、ますます高速なスイッチング速度が必要になります。 従来「遅い」測定器であっても、チューニング速度を上げる必要があります。 典型的な例は、4 つの独立した高速周波数シンセサイザーを備えた新しいベクトル ネットワーク アナライザーです。 したがって、周波数シンセサイザーの設計者はこの傾向を考慮する必要があります。 必要な調整速度はマイクロ秒の範囲です。

エネルギー消費量と寸法。 最新の機器は小型化され、エネルギー消費量が少なくなる傾向があります。 新しい設計では、高度な統合と低消費電力のチップを使用する必要があります。 また、かさばってエネルギーを大量に消費する YIG ジェネレーターやフィルターの使用もやめるべきです。

特別な要件

最新のマイクロ波周波数シンセサイザーには、技術的特性の継続的な改善、機能の拡張、サイズの縮小、消費電力、最終コストが必要です。 ただし、現代のマイクロ波システムのスループットの絶え間ない拡大により、調整速度を向上させる特別な要件が必要になります。 従来の計測および通信システムは依然としてミリ秒範囲で動作しますが、新しいシステムでは重要な特性 (位相ノイズ、非高調波歪み) を維持しながらマイクロ秒のスイッチング速度が必要であり、これは明らかに重大な技術的課題を引き起こします。 もう 1 つの問題は、最終コストの削減は、かなり「標準的な」要件ではあるものの、必要な技術的ソリューションの選択肢も大幅に狭めてしまうことです。

これらの特別な要件、つまりマイクロ秒範囲の調整速度 (低ノイズと低歪み!) および低コストは、新世代の周波数シンセサイザーの開発における重要なパラメータとなる可能性があります。

建築ソリューション

以下では、周波数シンセサイザーのさまざまなアーキテクチャと設計機能について説明します。 シンセサイザーのコストを削減するだけでなく、チューニング速度の向上を目的とした技術的ソリューションには特に注意が払われています。

アナログシンセサイザー。 シンセサイザーの主な機能は、基準信号 ( 参照) を必要な出力信号の数に合わせます。 アナログシンセサイザー ( 直接アナログシンセサイザー)は、図に示すように、個々の基本周波数とその後のフィルタリングを混合することによって実装されます。 1. 基本周波数は、乗算、除算、または位相ロック ループを通じて、低周波 (石英、界面活性剤) または高周波 (誘電体、サファイア、導波管、セラミック共振器) 発振器に基づいて取得できます。

このトポロジの主な欠点は、範囲と周波数分解能が制限されていることです。 この例 (図 1) では、(ミキサーの両方の側波帯を使用した場合でも) 18 個以下の出力周波数が生成されます。 図に示すように、より多くの基本周波数や混合ステージを導入することで、生成される信号の数を増やすことができます。 しかし、これにより使用されるコンポーネントの数が急速に増加し、その結果システムが複雑になります。

効果的な解決策は、デジタル ( DDS) シンセサイザー (図 3) を使用して、アナログ部分に必要な最小周波数ステップを増加させます。

|

もう 1 つの深刻な問題は、混合段階で大量の不要な変換生成物が発生することであり、これは慎重にフィルタリングする必要があります。 スイッチフィルターの必要な絶縁を確保するためには、特に注意を払う必要があります。 多数の異なるミキサおよびフィルタの設計が知られていますが、通常、小さなステップ サイズと広い周波数カバレッジを実現するには、ハードウェア (つまりコンポーネント) を集中的に使用する必要があります。 したがって、このアプローチは非常に高いチューニング速度と低ノイズを提供しますが、コストがかなり高いため、その使用は制限されています。

デジタルシンセサイザー。 従来のソリューションとは異なり、デジタル シンセサイザー ( DDS – ダイレクト デジタル シンセサイザー) デジタル処理を使用して、ベース (クロック) 信号から目的の出力波形を構築します。 位相アキュムレータを使用して、最初に信号のデジタル表現が作成され (図 4)、次にデジタル - アナログ コンバータ (DAC - DAC)。 デジタル信号の生成速度は主にデジタル インターフェイスによって制限され、アナログ回路に匹敵する非常に高速です。 デジタル シンセサイザーはかなり低い位相ノイズも提供し、使用されるクロック信号のノイズも減少します。 この観点から見ると、デジタル シンセサイザーは通常の分周器のように機能します。 ただし、デジタル シンセサイザーの主な利点は、位相バッテリーの長さによって決まる非常に高い周波数分解能 (1 Hz 未満) です。

|

主な欠点は、周波数範囲が限られていることと、信号の歪みが大きいことです。 デジタル シンセサイザーの動作周波数範囲の下限は実際には DC 領域にありますが、その上限はナイキスト基準に従ってクロック周波数の半分を超えることはできません。 さらに、出力信号の再構築にはローパス フィルターを使用する必要があり、出力信号の範囲がクロック周波数の約 40% に制限されます。

もう 1 つの深刻な問題は、望ましくないスペクトル積 ( スパーズ) 量子化と DAC 変換エラーが原因です。 この観点から見ると、デジタル シンセサイザーは周波数ミキサーのように動作し、組み合わせ周波数で個別の積を生成します。 これらの積の周波数位置は簡単に計算できますが、その振幅は予測しにくいです。 通常、低次の積の振幅が最も大きくなりますが、特定のシンセサイザーの周波数計画を設計する際には、かなり高次の積も考慮する必要があります。 クロック周波数が増加すると振幅も増加するため、生成される周波数の範囲がさらに制限されます。 範囲の上限の実用的な値は、離散スペクトル積 -50...-60 dBc のレベルで数十から数百 MHz の範囲にあります。 明らかに、スペクトル構成がさらに劣化するため、周波数シンセサイザ出力信号の直接逓倍は実現できません。

デジタル シンセサイザーのスペクトル構成を改善することを目的としたハードウェアおよびソフトウェア ソリューションが多数あります。 ハードウェアによる方法は通常、図に示すように、デジタル シンセサイザー信号の周波数を上げて分割することに基づいています。 5. この方法は、周波数分割プロセスに固有の 20 dB/オクターブの不要なスペクトル積を効果的に低減します。 残念ながら、これにより生成される信号の帯域幅も減少するため、アナログ回路と同様に、使用するベース周波数とフィルターの数を増やす必要があります (図 6)。

ソフトウェア手法は、デジタル シンセサイザーのディスクリート製品の位置が出力信号とクロック周波数の関数であるという事実に基づいて、シンセサイザーの周波数計画を最適化することを目的としています (周波数ミキサーと同様)。 したがって、与えられた出力周波数に対して、デジタル シンセサイザのクロック周波数を変更することによって、離散積を周波数シフトする (したがってフィルタリングする) ことができます。 この技術は、クロック生成と出力信号の狭帯域フィルタリングを提供する PLL システムで特に効果的に使用できます。 ソフトウェアによる方法は、比較的少量の製品を抑制するのに非常に効果的に機能することに注意してください。 残念ながら、離散スペクトル積の密度は通常、次数に比例して増加するため、この方法の実際の使用は -70...-80 dBn のレベルに制限されます。

|

したがって、デジタル シンセサイザーは周波数範囲が限られており、不要なスペクトル積が多く含まれるため、マイクロ波信号を直接生成するために使用されることはほとんどありません。 同時に、高周波数分解能を提供するために、より複雑なアナログおよび PLL システムで広く使用されています。

PLLシンセサイザー

フェーズロックループの使用に基づくシンセサイザーは、原則として、アナログ回路と比較してサイズと複雑さのレベルがはるかに小さくなります。 したがって、一般的なシングルループ PLL シンセサイザには、調整可能な電圧制御発振器 (VCO - VCO)、図に示すように、その信号は必要な(プログラム可能な)周波数分割の後、位相検出器の入力に供給されます。 7。

|

位相検出器のもう一方の入力は基準信号源 ( 参照)、その周波数は必要な周波数ステップに等しい。 位相検出器は両方の入力の信号を比較して誤差信号を生成します。この誤差信号は、フィルタリングと増幅(必要な場合)の後、VCO 周波数を ƒ=F REF × N に調整します。ここで、F REF は、入力端での基準信号の周波数です。位相検出器入力。

PLL ベースの回路の主な利点は、ローパス フィルター (LPF - LPF)、アナログ シンセサイザーと比較して複雑さのレベルははるかに低くなります。 主な欠点は、アナログ回路に比べてチューニング時間が長くなり (PLL フィルタの帯域幅、したがって周波数ステップに反比例します)、位相ノイズが大幅に高くなる点です。 PLL フィルター帯域幅内のシンセサイザーの位相ノイズは λ = λ です。 PD+20ログ Nここで、λ PD は、位相検出器の入力に対して再計算された、基準信号、位相検出器、分周器、フィルタおよびフィードバック回路アンプの総位相ノイズレベルです(図8)。 したがって、位相ノイズは分周器の分周比に依存し、必要な周波数分解能を提供するには分周比が非常に大きくなる可能性があります。 したがって、1 MHz の分解能で 10 GHz の周波数の信号を取得するには、分周係数は 10000 に等しくなければなりません。これは、80 dB の位相ノイズの増加に相当します。 さらに、プログラム可能な分周器は比較的低い周波数で使用されるため、固定分周比を持つ追加の高周波分周器の導入が必要になります。 (プリスケーラ)。これにより、フィードバック ループの合計分周比が増加し、その結果、位相ノイズがさらに悪化します。 明らかに、このような単純な回路では、最新の低ノイズ基準信号発生器のノイズ機能を使用できません。 さらに、シンセサイザーの出力スペクトル内の基準信号の高調波成分も、通常、フィードバック分周比に比例します。 結果として、シングルループ PLL 回路の使用は限られており、つまり、生成される信号の品質にそれほど要求を課さないシステムでのみ使用されます。

|

シンセサイザーの基本特性は、図に示すようにフィードバック回路に周波数変換(ミキサー)を導入することで大幅に改善できます。 この場合、VCO信号は周波数が下方に転送されるため、フィードバック回路の分周比を大幅に低減することができる。 ミキサー基準信号は、追加の PLL (マルチループ ループ) または周波数逓倍器を使用して生成されます。 優れた解決策は、内蔵ダイオードによって生成された基準信号の複数の高調波を使用する高調波ミキサーを使用することです。 ハーモニック ミキサーを使用すると、シンセサイザーの設計を大幅に簡素化できます。 同時に、このタイプのミキサーは個々の回路要素のパラメーターに非常に敏感であり、その最適化は決して簡単な作業ではないことに注意する必要があります。

|

位相ノイズと周波数分解能の特定の要件に応じて、より多くのミキシング ステージを導入することも可能ですが、これによりシンセサイザーの設計がより複雑になります。 周波数変換ベースの回路に固有のもう 1 つの問題は、誤った周波数ロックです (たとえば、ミキサー ミラー チャネルを使用する場合)。 これには、たとえばデジタル - アナログ コンバータ (DAC) を使用するなど、VCO 周波数をかなり正確に事前調整する必要があります。 そのため、動作温度範囲にわたる VCO の周波数同調特性の極めて高い直線性 (および再現性) と、温度ドリフトを補償するためのこの特性の正確な校正が必要となります。 さらに、デジタル - アナログ コンバータは通常、ノイズ レベルが高いため、シンセサイザのノイズ特性に直接影響を及ぼし、必要な周波数に事前に調整した後、DAC を PLL ループから削除する必要があります。

総除算係数を減らすもう 1 つの方法は、分数除算係数の使用に基づいており、これは周波数を N+1 毎 M信号の周期と除算 N残りの期間中。 この場合、平均除算係数は次のようになります。 (N+1)/ M、 どこ Nそして M- 整数。 所定の周波数ステップ サイズに対して、分数除算回路により、位相検出器の入力でより高い比較周波数を使用できるようになり、位相ノイズが減少し、シンセサイザの同調速度が向上します。 分数除算技術の主な欠点は、分数除算メカニズムに固有の位相誤差により、非調和スペクトル成分の含有量が増加することです。

非常に効果的な解決策は、上で説明したデジタル シンセサイザーを使用することです ( DDS)、これも本質的には分数分周器です。 図に示すように、デジタル シンセサイザーは基準信号源または分数分周器として使用できます。 それぞれ10、11。 デジタル シンセサイザー出力信号のスペクトル構成には特に注意を払う必要があります。PLL ループに分周器が存在するため、この信号は 20 dB/オクターブ劣化します。 この観点から見ると、図のような構成になります。 10 は、上で説明した混合段階の導入を可能にするため、より柔軟であるように見えます。 図に示されている図ですが、 ただし、デジタル シンセサイザの入力 (クロック) 周波数と出力周波数の比率に応じて、同じ程度の劣化が発生します。

|

|

デジタル シンセサイザーのスペクトル特性を改善するための上記の方法は、非常に高いフィルター特性を持つ PLL 回路と効果的に機能することに注意してください。 また、デジタル シンセサイザーの使用により回路はある程度複雑になりますが、それでも全体的な設計は技術的およびコスト的に優れたものになると思われます。

VCOの選択

PLL シンセサイザーの設計は、使用される VCO のパラメーターによって主に決定されます。 歴史的に、シンセサイザーの開発者は主に YIG 発振器に依存してきました。YIG 発振器は、生成される周波数の範囲が広く、位相ノイズが低いという特徴があります。 YIG 発振器は線形 (再現性のある) チューニング特性も示し、マルチループ PLL システムでの初期チューニングと周波数ロックを容易にします。 YIG オシレーターのこれらのユニークな機能により、YIG オシレーターをベースにしたシンセサイザーの優位性が長い間保証されてきました。

しかし、エネルギー消費量が多く、サイズが大きく、コストが高く、特に YIG 発電機に固有のチューニング速度が遅いため、半導体発電機への移行が決定されました。 現在、高周波 (最大 10 GHz 以上) ソリッドステート調整可能発振器は、安価な集積回路の形で入手可能です。 このような発振器のノイズ特性は YIG 発振器に比べて著しく悪いため、シンセサイザーの設計者は主に基準信号源のノイズ特性に依存する必要があります。 現在、市販の水晶発振器は、周波数 100 MHz、オフセット 20 ~ 100 kHz で -160 ~ -176 dBc/Hz の範囲の位相ノイズを示します。 これらの値は、10 GHz および同じ離調周波数に変換すると -120...-136 dBc/Hz に相当し、YIG 発生器のノイズ特性に匹敵し、さらに優れています。 もちろん、個々のシンセサイザー要素のノイズ特性は、基準信号の変換プロセスに顕著な影響を与えないと想定されます。 この仮定には創造的なエンジニアリングが必要ですが、最終結果は明らかです。半導体発振器をベースにしたシンセサイザーは、高価でかさばり、電力を大量に消費する YIG 発振器を使用せずに、優れたノイズとスペクトル性能とともに非常に高いチューニング速度を達成できる可能性があります。

今後の展開

アナログ シンセサイザーは今日最も先進的なアーキテクチャであり、非常に高いチューニング速度と低い位相ノイズを提供します。 アナログ シンセサイザのコスト特性はコスト削減の一般的な傾向に対応していませんが、それでも、低コストが主要な要素ではない一部のアプリケーションでは、アナログ シンセサイザは優れたソリューションとなる可能性があります。 デジタル シンセサイザーの動作周波数が増加すると、アナログ シンセサイザーの設計が簡素化されるため、ある程度のコスト削減が期待されます。

GaAs、Si、SiGe テクノロジーの極めて急速な発展の結果、デジタル シンセサイザーには大きな可能性が秘められています。 デジタルシンセサイザーの動作周波数やスペクトル特性は向上し、アナログシンセサイザーやPLLシンセサイザーの設計に大きく役立つことが期待されています。

しかし、近い将来最も有望な開発は、明らかに、安価な発振器集積回路をベースにした PLL シンセサイザーに関連するものとなるでしょう。 主な取り組みは、シンセサイザーの個々の要素の固有ノイズを低減して、PLL フィルターの最適帯域幅を数 MHz まで拡張することを目的としています。この帯域幅では、固体発振器はノイズ特性において YIG 発振器と競合するようになります。 これにより、YIG 発生器に固有のノイズ レベルを維持しながら、マイクロ秒範囲の周波数調整速度を達成することが可能になります。 これらの特性は、PLL シンセサイザーに固有の低コストとともに、将来の設計における PLL シンセサイザーの優位性を事前に決定する可能性があります。

文学:

- J. Browne、「周波数シンセサイザーの通信システムの調整」、Microwaves&RF、2006 年 3 月。

- V. Kroupa、「周波数合成理論、設計、および応用」、ニューヨーク:ウィリー、1973 年。

- V. Manassewitsch、「周波数シンセサイザーの理論と設計」、第 3 版、ニューヨーク: John Wiley & Sons、1987 年。

- U. ローデ、「マイクロ波およびワイヤレス シンセサイザー: 理論と設計」、ニューヨーク: John Wiley & Sons、1997 年。

- J. Klapper および J. Frankle、「位相ロックおよび周波数フィードバック システム」、ニューヨーク: ワイリー、1972 年。

- 「A 24 GHz Network Analyzer」、ローデ・シュワルツ著、Microwave Journal、2005 年 10 月。

- Z. Galani および R. Campbell、「レーダー用周波数シンセサイザーの概要」、IEEE Transactionson Microwave Theory and Techniques、vol. MTT-39、1991、pp. 782-789。

- V. Kroupa、「ダイレクト デジタル周波数シンセサイザー」ニューヨーク: IEEE Press、1999 年。

- T. Endres、R. Hall、および A. Lopez、「軍事宇宙搭載アプリケーション向けの DDS ベースのシンセサイザーの設計と解析方法」、IEEE 国際周波数制御シンポジウム議事録、1994 年、pp. 625-632。

- W. イーガン、「位相ロックによる周波数合成」ニューヨーク: Wiley、2000 年。

- R. ベスト、「位相ロック ループ - 理論、設計、およびアプリケーション」ニューヨーク: マグロウヒル、1984 年。

- U. Rohde、「デジタル PLL シンセサイザー: 設計とアプリケーション」ニュージャージー州: プレンティス ホール、1983 年。

- A. ブランチャード、「位相ロック ループ」、ニューヨーク: ワイリー、1976 年。

- F. Gardner、「Phaselock Techniques」第 2 版、ニューヨーク: Wiley、1979 年。

- 「フラクショナル N シンセサイザー」アプリケーション ノート、Synergy Microwave Corporation、 http://www.synergymwave.com/> www.synergymwave.com.

- 「A High Frequency Reference Module」、Valpey Fisher Corporation、Microwave Journal、2005 年 4 月。

著者について

Alexander Chenakin はキエフ工科大学を卒業し、技術科学の候補者となりました。 彼はさまざまなエンジニアリングおよび管理職を歴任し、マイクロ波信号生成分野の先進技術を研究するコンサルティング会社を率いました。 彼は現在、米国サンノゼにあるフェーズ マトリックス社の周波数合成部門のディレクターとして勤務しており、さまざまな測定機器やシステム向けの新世代の周波数シンセサイザーの開発を監督しています。

最高のメーカーの製品を提供します

PRIST は測定の問題に対する最適なソリューションを提供します。

当社では、オシロスコープ、電源、信号発生器、スペクトラム・アナライザ、校正器、マルチメータ、電流クランプを購入できるだけでなく、測定器の検証や校正も行うことができます。 当社は世界最大手の計測機器メーカーと直接契約を結んでいるため、お客様の課題を解決する機器を選定することができます。 豊富な経験から、以下のブランドの製品をお勧めします。

トランシーバーデバイスの周波数安定性の問題は常に存在します。 比較的低い周波数(最大 100 ~ 150 MHz)では水晶共振器を使用して問題を解決し、より高い周波数(400 MHz)では表面弾性波に基づく共振器(SAW 共振器)を使用し、超高周波を安定させるために高周波で作られた誘電体共振器を使用しました。セラミックやその他の高 Q 共振器など、高品質の材料がよく使用されます。 説明した受動部品を使用した安定化方法には、実装が簡単で比較的低コストであるという利点がありますが、主な欠点は、周波数設定要素である共振器を変更せずに大幅な周波数調整が不可能であることです。 安定性を維持しながら動作周波数を迅速に電子的に調整することは不可能であるため、無線デバイスの使用が大幅に制限され、たとえばマルチチャネルの実装が不可能になります。

現在広く使用されているさまざまな外国企業の統合型周波数シンセサイザーは、高い安定性を維持しながら、超高周波を含む動作周波数の迅速な電子調整を可能にします。 このような周波数シンセサイザーには、直接タイプと間接タイプがあります。 直接合成の利点には、小さい周波数グリッド ステップでの高性能が含まれますが、多数の非線形信号変換によって生じる多数のスペクトル成分をフィルタリングする必要があるため、直接合成デバイスがマイクロ波回路で使用されることはほとんどありません。 超高周波を合成するには、通常、間接シンセサイザーまたはフェーズ ロック ループ (PLL) シンセサイザーが使用されます。 PLL を備えた統合シンセサイザーには、主に 2 つのタイプがあります。周波数値が 3 線バスを介して外部マイクロコントローラーによって設定されるプログラマブルタイプと、内部分周器の分周係数が固定される非プログラマブルタイプです。基準周波数は外部水晶共振器によって設定されます。 単純なマイクロ波回路では、通常、プログラマブルではない統合型シンセサイザー (たとえば、Motorola の MC12179) が使用されますが、その欠点には、常に可能であるとは限らない水晶共振器を正確に選択する必要があることが含まれます。 Philips の UMA1020M などのプログラマブル周波数シンセサイザーにはこの欠点がなく、最新の通信システムには常に制御マイクロコントローラーがあるため、このようなシンセサイザーのプログラミングは技術的に簡単です。 超高周波範囲の自動発電機は、ハイブリッド技術を使用して作成された機能的に完全なモジュールの形で使用されます。

説明されているソリューションの応用例は、この記事で提案されている、1900 ~ 2275 MHz の範囲の周波数を高精度で生成および安定化できる、単純な実験用超高周波シンセサイザーです。

設計したシンセサイザーのブロック図を図に示します。 1.、外観 - 図2。 回路を見るとわかるように、このシンセサイザーは、Mini-Circuits JTOS-2200 の電圧制御発振器 (VCO または VCO) JTOS-2200、統合周波数シンセサイザー UMA-1020M、および Zilog のマイクロコントローラー Z86E0208PSC で構成されています。

VCO によって生成されたマイクロ波信号は、ラボ用シンセサイザーの出力と、UMA-1020M 回路に含まれるメインのプログラマブル分周器の入力に供給されます。

JCO-8 水晶発振器によって生成された基準信号は、同じく UMA-1020M 回路に含まれる補助プログラマブル分周器に供給されます。 UMA-1020Mのブロック図を図に示します。 3、UMA-1020M の詳細な技術文書は、メーカーの Web サイト http://www.philips.de/ でご覧いただけます。 メインと補助の両方の分周器の係数は、3 線式 (DATA データ、CLK 同期、書き込み許可 / ENABLE) バスを介して Z86E0208PSC マイクロコントローラーによって設定されます。 Z86E0208PSC マイクロコントローラのブロック図を図に示します。 4. マイクロコントローラーの内部 ROM は、7 つの異なる周波数値と 1 つのテスト モードをプログラムするのに十分です。 特定の周波数値(またはテストモード)は、実験室用シンセサイザーのプリント基板上のジャンパによって設定されます。 次の周波数値を統合シンセサイザーにロードする前に、マイクロコントローラーはジャンパーに接続されているポートをポーリングし、受信したデータに従って 1 つまたは別のファームウェアを選択します。 新しい周波数値は、シンセサイザー ボードの電源がオンになると自動的に設定されます。 Z86E0208PSC マイクロコントローラーのシンセサイザー プログラミング アルゴリズムを図に示します。 図5に番組リストが示される。

Zilog マイクロコントローラーのプログラミングの詳細については、Web サイト http://www.zilog.com/ で完全な技術文書を参照してください。

使用される JTOS-2200 VCO の特別な機能は、0.5 ~ 5 ボルトの同調電圧範囲です。 つまり、設定電圧値が 0.5 ボルト未満の場合、メーカーは安定した発振の発生を保証しません。 実行された実験は、この声明の真実性を示しました。

PLL の動作原理とフィードバック フィルター (ループ フィルター) の計算方法は、技術文献で広く繰り返し議論されているため、この記事では説明しません。 フィードバック フィルター パラメーターを計算できる無料で利用できるプログラムがいくつかあり、インターネットの http://www.analog.com/ または www.national.com で見つけることができます。

シンセサイザー回路の正しい動作を監視するために、LED がボードに取り付けられており、その光りは周波数合成のエラーを示します。 シンセサイザーが正常に動作している場合、LED は点灯しませんが、この機能はソフトウェアで無効にすることができます。

組み立てられた実験用シンセサイザーのコストは 30 ドルを超えません。 提案されたデバイスのコストを削減するには、2 つの方法が提案できます。まず、Z86E0208PSC の最大クロック周波数が 8 MHz であることを念頭に置きながら、シンセサイザーとマイクロコントローラーの水晶基準発振源を組み合わせることができます。 -1020M は 5 ~ 40 MHz の範囲内になります。 第 2 に、VCO は、ここで説明した方法論を使用して、トランジスタまたは増幅集積回路を使用して独立して開発できます。

中古文献リスト

- 誘電体共振器 / M.E. イルチェンコ、V.F. ヴジャティシェフ、LG. ガサノフら。 エド。 自分。 イルチェンコ。 – M.: ラジオと通信、1989. – 328 p.: 病気。 – ISBN 5-256-00217-1。

- ペストリヤコフ A.V. 合成および周波数安定化デバイス用の集積回路 // チップ ニュース。 – 1996年。 – No. 2。

- Lobov V.、Steshenko V.、Shakhtarin B. 直接周波数合成用のデジタル シンセサイザー // チップ ニュース。 – 1997年。 – 第1位。

- ワイヤレス半導体ソリューション。 モトローラ。 デバイスデータ – Vol.1。 DL 110/D、Rev 9。

- VCO デザイナーズ ハンドブック 2001。VCO/HB-01。 ミニサーキット。

- グラッドスタイン MA Zilog の Z86 ファミリのマイクロコントローラー。 プログラマーズガイド。 - M.: DODEKA、1999、96 p.

- Z8 アプリケーション ノート ハンドブック。 ジログ。 DB97Z8X0101。

- Starikov O. PLL の方法と高周波信号の合成原理//チップ ニュース。 – 2001年。 – No. 6。

- マイクロ波発振器の設計。 アプリケーションノート A008// Hewlett-Packard Co. - 出版番号 5968-3628E (1999 年 6 月)

- Shveshkeyev P. 2.4 ~ 2.5 GHz ISM 帯域の WLAN アプリケーション向け VCO 設計//応用マイクロ波とワイヤレス。 – 2000年。 – No. 6。 – P.100〜115。

マイクロ波装置を開発および設定する場合、アマチュア無線家は、必要な周波数範囲の測定機器が不足しているために困難に遭遇することがよくあります。 提案された周波数シンセサイザーはアマチュア条件でも作成できます。 1900 ~ 2275 MHz の範囲で動作します。 周波数値は、スイッチを使用していくつかの可能な値から選択されます。

比較的低い周波数 (最大 100 ~ 150 MHz) では、発電機の周波数を安定させるという問題は水晶共振器を使用することで解決され、より高い周波数 (400 MHz) では表面弾性波上の共振器 (SAW 共振器) を使用することで解決されます。マイクロ波周波数では、高品質セラミックからの誘電体共振器やその他の高品質共振器が使用されます。 受動コンポーネントを使用した安定化には、実装が簡単で比較的低コストであるという利点があります。 その主な欠点は、周波数設定要素を変更せずに、生成される信号の周波数を大幅に変更することができないことです。

広く普及している統合型周波数シンセサイザーにより、高周波数の安定性を維持しながら、発生器 (マイクロ波を含む) の高速電子チューニングを実装することが可能になります。 シンセサイザーには直接タイプと間接タイプがあります。

直接合成の利点は、周波数変更の高速性と小さなステップでのチューニングであると考えられます。 ただし、合成信号には多数の非線形変換から生じる多数のスペクトル成分が存在するため、マイクロ波機器では直接合成デバイスが使用されることはほとんどありません。

マイクロ波合成には、フェーズ ロック ループ (PLL) を備えた間接シンセサイザーがよく使用されます。 PLL の動作原理とフィードバック フィルターを計算する方法は、たとえば次のような文献で広く繰り返し議論されています。 フィードバック フィルターの最適なパラメーターを計算できる無料配布プログラムがいくつかあり、インターネット上の次の場所にあります。

PLL を備えた統合シンセサイザーには、プログラマブル (外部コマンドによって周波数値を設定) と非プログラマブル (基準周波数の固定の逓倍係数および除算係数を変更できない) の 2 つのタイプがあります。

MC12179 などのプログラム不可能な統合型シンセサイザーの欠点には、正確に指定された周波数を持つ水晶共振器を使用する必要があることが含まれますが、これは常に可能であるとは限りません。 UMA1020M などのプログラマブル シンセサイザーにはこの欠点はありません。 制御用マイクロコントローラーをお持ちの場合、このようなシンセサイザーを特定の周波数に設定することは技術的に簡単です。 シンセサイザーマイクロ回路との連携に必要な電子周波数チューニングを備えたマイクロ波自励発振器は、ハイブリッド技術を使用して作られた機能的に完全なモジュールの形で消費者に入手可能です。

2 GHz 範囲の機器の設定を確認および調整することを目的とした実験用周波数シンセサイザーの図を図 1 に示します。その基礎となっているのは UMA-1020M (DA3) マイクロ回路であり、その技術文書は次の URL で見つけることができます。メーカーの Web サイト

シンセサイザーには、電圧制御発振器 (VCO) DA1、10 MHz 水晶発振器 DA2、およびマイクロコントローラー DD1 も含まれています。 VCO の出力からのマイクロ波信号は、シンセサイザーの出力 (コネクタ XW1) と、DA3 チップのメイン プログラマブル分周器の入力に送られます。 DA2 発生器の出力からの基準周波数信号は、DA3 マイクロ回路の一部である補助プログラマブル分周器に供給されます。

メインおよび補助分周器の分周係数はマイクロコントローラ DD1 (Z86E0208PSC) によって設定され、3 線情報バス (ピン 11 ~ 13 DA3) を介して対応するコマンドを送信します。 制御プログラムのソーステキストを表に示します。 1. マイクロコントローラの内部メモリは、7 つの異なる周波数値に関するデータを保存するのに十分です。 周波数値の 1 つ、または出力に信号がないモードは、表に従ってジャンパ S1 ~ S3 を使用して選択されます。 2. セットモードは装置の電源を入れた瞬間に有効となり、その後は再度電源を入れるまでスイッチを操作しても動作に影響を与えません。 HL1 LED は電源投入後 1 秒後に消灯します。 Zilog マイクロコントローラーのプログラミングについては、で読むことができます。

シンセサイザーはプリント基板上に組み立てられており、その外観を図に示します。 2. 表面実装抵抗とコンデンサを使用しています。

文学

- Starikov O. PLL の方法と高周波信号を合成する原理。 - チップニュース、2001 年、第 6 号。

- VCO デザイナーズ ハンドブック 2001. VCO/HB-01. - ミニ回路。

- Glvdshtein M. A. Zilog の Z86 ファミリのマイクロコントローラー。 プログラマーズガイド。 - M.: DODEKA、1999、96 p.

UMA1020M チップには、マイクロ波シンセサイザに加えて、20 ~ 300 MHz の周波数範囲で動作するもう 1 つのシンセサイザが含まれています。6n は、説明されている設計では使用されていません。