실험실 마이크로파 합성기. 계획, 설명

§ 1.10에서 다음과 같이 원칙적으로 마이크로파를 포함한 모든 주파수 범위에서 디지털 위상 고정 루프를 사용하여 DKSCH 시스템을 구축하는 것이 가능합니다. 비록 데시미터 범위(예: , )에 불과하지만 이러한 시스템에 대한 잘 알려진 출판물은 60년대 후반으로 거슬러 올라갑니다. SMV 범위에 관해서는 이 범위의 디지털 신디사이저를 설명하는 1971년 기사가 단 하나뿐입니다. 최대 400MHz 범위의 신디사이저는 미터 파장 범위에 속하며 미터 한계보다 약간 더 큰 범위를 포괄할 뿐만 아니라 구성 원리에 따라 더 가깝다는 데 동의합시다.

가장 단순한 디지털 신디사이저의 작동 주파수 범위 폭은 DPCD의 최대 속도를 초과할 수 없기 때문에 실제로 가장 간단한 DLL 시스템은 마이크로파에 적용할 수 없습니다. 위에서 DPKD를 켜기 전에 DPKD를 켜면 시스템이 더 관성화되고 후자의 소음 특성이 악화된다는 점을 언급했습니다. 실제로 최신 DPCD의 최대 속도가 약 50MHz라면 f 0 = 5GHz(센티미터 범위의 중간)에 대해 분할 계수 c = 100인 DPCD가 필요합니다. 즉, 다른 조건이 동일하다면 대역은 다음과 같습니다. 이 예에서는 DPLLL 링의 크기가 두 자릿수만큼 좁아집니다.

§ 1.10에서 볼 수 있듯이 헤테로다인 DFLL 시스템(그림 1.12c)은 비록 부피가 더 크지만 가장 단순한 시스템보다 열등하지 않은 전기적 특성을 가지고 있습니다. DPKD의 속도에 의해 제한되지 않으므로 마이크로파 합성기에 사용할 수 있습니다. 그러나 전자레인지에 이 시스템을 사용하는 데에는 고유한 특성이 있습니다. 첫째, 마이크로파에서 작동 주파수 범위 P 0 = f 0 max - f 0 min의 폭은 거의 항상 DPKD f DP max의 속도를 초과하므로 헤테로다인은 하나의 주파수가 아닌 기준 그리드에 의해 수행되어야 합니다. 주파수 f q (k) (이전 10년의 다중 10년 DKSCH 시스템에서와 같이). 둘째, 지정된 그리드 β k의 이산성 단계는 DPKD f DP max - f DP min의 안정적인 분할 범위의 너비를 초과해서는 안 됩니다. 즉, 실질적으로 β k f DP max - f DP min, 그런 다음 DPKD 이전에 하나 또는 두 개의 트리거 형태로 DPKD를 켜야 합니다. DPKD의 이러한 작은 분할 계수(c = 2 또는 c = 4)는 첫째로 시스템의 전기적 특성을 눈에 띄게 저하시키지 않으며, 둘째로 업계에서 더 빠르게 작동하는 DPKD를 개발함에 따라 DFKD는 먼저 단일 트리거(c = 2)이므로 체계에서 완전히 제외될 수 있습니다.

따라서 디지털 합성기의 일반적인 마이크로파 블록 다이어그램은 그림 1과 같이 묘사될 수 있습니다. 3.1a. 이 시스템의 경우

(3.1)과 (3.2)의 결합 솔루션은 다음을 제공합니다.

그런 다음 (3.3)과 (3.4)에서 DPKD의 분할 계수를

두 번째 장에서는 기준 주파수를 선택하기 위한 기준[형식(2.44)]을 정의하여 합성기 출력에서 PLL 링에 의해 제어되지 않는 측면 구성 요소가 없음을 보장했습니다. 그림 1의 다이어그램에서 이러한 기준이 어떻게 충족되는지 살펴보겠습니다. 3.1a. 왜냐하면

그런 다음 (3.6)을 (3.1)로 대체하면 다음을 얻습니다.

(2.44)로부터 조건을 만족하는 것이 필요하다는 결론이 나옵니다. ![]() 마지막 표현(불평등을 평등으로 대체)에서 극단적인 경우를 취하고 이를 고려하여 (3.8)을 (3.7)로 대체하면 다음이 나타납니다.

마지막 표현(불평등을 평등으로 대체)에서 극단적인 경우를 취하고 이를 고려하여 (3.8)을 (3.7)로 대체하면 다음이 나타납니다.

그러나 일반적으로 마이크로파 시스템에서는 P 0 >> f DC max. 따라서 DFCD 분할 계수는 충분히 크게 선택되거나 그림 1의 시스템에서 조건(2.44)을 선택해야 합니다. 3.1a는 특별한 경우에만 이행될 수 있습니다.

그러나 여기서는 동일한 결론에 도달할 수 있다는 것이 인정되었습니다.

시스템 매개변수에 대한 DFCD의 부정적인 영향은 특히 c에서 크게 나타났습니다. 가까운 장래에 DPKD의 성과가 급격히 향상될 것이라고는 기대할 수 없습니다. 따라서 시스템은 Fig. 3.1a는 협대역 합성기에서만 사용할 수 있습니다.

부등식(2.44) 중 하나를 충족하는 것이 필수이므로 기준 주파수 f" q "up" 또는 "down"을 합성기의 작동 범위 이상으로 옮겨야 하며, 합성기가 수신기에서 작동하는 경우 또는 송신기 믹서, 그러면 무선 링크의 반송파 주파수 작동 범위를 벗어납니다. 이 경우, 분명한 바와 같이 조건(2.44)은 하나 이상의 부등식으로 보완되어야 합니다.

특허 RU 2580068 소유자:

본 발명은 무선 공학에 관한 것이며 마이크로파 주파수 범위의 장치를 송신 및 수신하는 데 사용될 수 있습니다. 기술적인 결과는 입력되는 마이크로파 신호의 주파수를 튜닝할 때 안정적인 동작을 높이는 것입니다. 마이크로파 주파수 합성기는 마이크로파 전압 제어 발진기(VCO), 방향성 결합기, 마이크로파 믹서, 입력 마이크로파 신호 소스, 가변 분배 계수를 갖는 첫 번째 주파수 분배기, 주파수-위상 검출기, 두 번째 주파수를 포함합니다. 가변 분배 계수, 기준 신호 소스 및 필터가 있는 분배기 저역 통과, 위상 비교기, 대기 멀티바이브레이터, 다이오드 2개 및 연산 증폭기. 4 병.

본 발명은 무선 공학, 즉 마이크로파의 광범위한 위상 고정 루프(PLL) 시스템에 포함된 마이크로파 전압 제어 발진기(VCO)의 예비, 초기, 주파수 설정을 갖춘 광범위한 마이크로파 주파수 합성기에 관한 것입니다. 주파수 합성기는 마이크로파 주파수 범위의 트랜시버 장치에 사용될 수 있습니다.

합성된 주파수의 진동이 위상 고정 루프 형태의 능동 필터를 사용하여 필터링되는 능동 주파수 합성 시스템이 알려져 있습니다. 이 경우 신호 주파수는 예를 들어 저주파 범위로 분할되어 기준 발진기의 주파수와 비교되고 전압 제어 마이크로파 발진기(VCO)의 자동 튜닝 전압은 다음과 같습니다. 생성되었습니다. 능동 합성 시스템은 스퓨리어스 스펙트럼 성분과 반송파의 위상 잡음을 더 효과적으로 억제합니다. 그러나 이 회로에서는 VCO의 높은 주파수 분할 비율로 인해 합성기 출력 신호에서 낮은 잡음 레벨을 달성하는 것이 불가능합니다.

능동 합성 원리를 PLL 루프로 구현하는 마이크로파 주파수 합성기가 알려져 있으며, 제안된 발명의 프로토타입으로 선택되었습니다. 마이크로파 주파수 합성기는 마이크로파 VCO를 포함하며, 그 출력은 방향성 결합기를 통해 마이크로파 주파수 합성기의 출력과 마이크로파 믹서의 첫 번째 입력에 연결되고, 두 번째 입력은 소스의 출력에 연결됩니다. 주파수 f 마이크로파 입력을 갖는 입력 마이크로파 신호의 마이크로파 믹서의 출력은 가변 분할 계수 n을 갖는 첫 번째 주파수 분배기(DF)의 입력에 연결되고, 그 출력은 주파수의 첫 번째 입력에 연결됩니다. - 위상 검출기(FPD), 주파수-위상 검출기의 제2 입력은 가변 분할 계수 m을 갖는 제2 주파수 분배기의 출력에 연결되고, 그 입력은 기준 주파수 신호 fOP의 소스에 연결되며, 주파수 위상 검출기의 출력은 저역 통과 필터(LPF)를 통해 마이크로파 VCO의 입력에 연결됩니다. 이 경우 방향성 커플러, 믹서, 첫 번째 주파수 분배기, PFD 및 저역 통과 필터가 PLL 루프를 형성합니다.

공지된 마이크로파 주파수 합성기는 주파수가 있는 마이크로파 주파수 합성기의 입력 신호로 사용될 때 제1 주파수 분주기의 분주 계수를 줄여 주파수 f MF 를 갖는 마이크로파 주파수 합성기의 출력 신호에서 낮은 수준의 위상 잡음을 달성할 수 있게 한다. f 위상 잡음이 낮은 마이크로파 신호를 입력합니다. 또한 첫 번째 주파수 분배기의 분할 비율을 줄이면 PLL 루프의 이득을 높일 수 있습니다. 이러한 회로에서 마이크로파의 입력 마이크로파 신호 f의 주파수는 마이크로파의 조건 f >f MF에서 선택되므로 마이크로파 주파수 합성기의 PLL 루프 이득의 일정한 값을 유지하려면 다음이 필요합니다. PLL 루프 제어 대역을 유지하기 위해서는 마이크로파 VCO의 주파수 튜닝 기울기를 변경하여 첫 번째 주파수 분배기의 분배 계수의 변화를 보상해야 합니다.

그러나 VCO 마이크로파 VCO의 주파수 드리프트가 2f IF보다 큰 경우(중간 주파수 f IF = f 입력 마이크로파 - f VCO) 이 마이크로파 주파수 합성기에서 위상 동기화 오류가 발생하여 기능 손실이 발생합니다. 신디사이저의.

또한, 알려진 마이크로파 주파수 합성기는 마이크로파 입력의 고정 주파수를 갖는 입력 마이크로파 신호가 마이크로파 믹서의 두 번째 입력에 공급되는 경우에만 작동합니다. 마이크로파에서 가변(조정 가능한) 주파수 f를 갖는 입력 마이크로파 신호가 2f IF보다 크거나 같은 대역에서 마이크로파 믹서의 이 입력에 공급되면 마이크로파 주파수 합성기에서도 위상 동기화 위반이 발생할 수 있습니다.

본 발명의 기술적 목적은 위상 잡음이 낮고 합성기 f MF의 출력 신호 주파수에 대한 짧은 튜닝 시간을 갖는 광범위한 마이크로파 주파수 합성기를 생성하여 다음과 같은 경우 위상 동기화 위반이 없음을 보장하는 것입니다. 입력 마이크로파 신호 f 입력 마이크로파의 주파수를 중간 주파수 신호 f IF의 주파수의 두 배 이상인 대역에서 변경(튜닝)하고 f IF = f 입력 마이크로파 -f VCO를 보존합니다. 마이크로파 VCO 신호의 주파수 f VCO가 2f IF 이상 이동할 때 위상 동기화.

기술적 결과는 PLL 루프의 과도 프로세스로 인한 위상 동기화 위반을 방지하고 마이크로파 입력 신호의 주파수 f 입력 튜닝을 포함하여 작동 중에 마이크로파 주파수 합성기의 안정적인 작동을 보장하는 것입니다.

기술 솔루션의 핵심은 제안된 마이크로파 주파수 합성기에 전압 제어 마이크로파 발진기(VCO)가 포함되어 있으며, 그 출력은 방향성 커플러의 입력에 연결되고 첫 번째 출력은 마이크로파 주파수의 출력이라는 것입니다. 합성기 및 지향성 커플러의 두 번째 출력은 마이크로파 믹서의 첫 번째 입력에 연결되고, 마이크로파 믹서의 두 번째 입력은 입력 마이크로파 신호 소스의 출력에 연결되고, 마이크로파 믹서의 출력은 연결됩니다. 가변 분할비를 갖는 제1 주파수 분배기의 입력, 그 출력은 주파수-위상 검출기의 제1 입력에 연결되고, 주파수-위상 검출기의 제2 입력은 다음과 같이 제2 주파수 분배기의 출력에 연결됩니다. 입력이 기준 신호 소스의 출력에 연결되고 저역 통과 필터가 주파수 위상 검출기와 마이크로파 VCO 사이에 연결되는 가변 분할 비율. 마이크로파 주파수 합성기에는 위상 비교기, 대기 멀티바이브레이터, 다이오드 2개 및 연산 증폭기가 추가로 포함되어 있습니다. 이 경우, 주파수 위상 검출기의 제1 및 제2 출력은 각각 연산 증폭기의 제1 및 제2 입력에 연결되며, 그 출력은 마이크로파 VCO의 입력에 연결되고 저역 통과 필터는 연산 증폭기의 첫 번째 입력과 그 출력 사이에 연결되고, 위상 비교기의 첫 번째 입력은 가변 분배 계수를 가진 첫 번째 주파수 분배기의 출력과 주파수 위상 검출기의 첫 번째 입력에 연결되고, 두 번째는 위상 비교기의 입력은 가변 분할 계수를 갖는 두 번째 주파수 분배기의 출력에 연결되고 주파수-위상 검출기의 두 번째 입력에는 위상 비교기의 출력이 대기 멀티바이브레이터의 입력에 연결됩니다. 대기 멀티바이브레이터의 출력은 제1 다이오드를 통해 주파수-위상 검출기의 제1 출력과 연산 증폭기의 제1 입력에 연결되고, 대기 멀티바이브레이터의 두 번째 출력은 제2 다이오드를 통해 주파수의 제2 출력에 연결된다. -위상 검출기와 연산 증폭기의 두 번째 입력에 연결됩니다. 또한, 제1 및 제2 다이오드는 서로 반대 방향으로 연결되며, 마이크로파 VCO, 방향성 커플러, 마이크로파 믹서, 제1 주파수 분배기, 주파수 위상 검출기, 연산 증폭기 및 저역 통과 필터가 PLL(위상 고정 루프)을 형성합니다. : T M - τ m >τ PLL, 여기서 T M은 대기 중인 멀티바이브레이터의 발진 주기이고, τ PLL은 위상 고정 루프에서 동기화를 설정하는 시간입니다.

마이크로파 주파수 합성기의 회로 출력에 2개의 연속 다이오드가 있는 위상 비교기와 대기 멀티바이브레이터를 포함하면 다음과 같은 경우에 마이크로파 VCO의 VCO 신호의 주파수 f를 사전 설정할 수 있습니다. 입력 마이크로파 신호의 주파수 f를 전환하거나 마이크로파 VCO 신호의 주파수 f VCO를 떠날 때(예: 마이크로파 합성기를 켤 때) 발생하는 PLL 루프의 위상 동기화 위반으로 인해 위상 동기화의 신속한 복원이 보장됩니다. 마이크로파 주파수 합성기의 안정성을 높입니다. 이 경우 PLL 루프가 복원된 후 대기 멀티바이브레이터가 꺼지고 PLL 루프의 추가 작동에 영향을 주지 않습니다.

피드백 회로에 저역 통과 필터가 있는 연산 증폭기는 PLL 루프의 제어 대역폭을 형성합니다.

이 멀티바이브레이터의 RC 회로에 의해 결정되는 대기 멀티바이브레이터의 첫 번째 펄스 끝과 다음 펄스 시작 사이의 시간은 PLL 루프에서 동기화를 설정하는 데 걸리는 시간보다 커야 합니다. 조건이 충족되어야 합니다:

T M -τ m >τ PLL.

본 발명은 도면으로 예시된다.

그림에서. 그림 1은 제안된 마이크로파 주파수 합성기의 블록 다이어그램을 보여줍니다.

1 - 주파수 f VCO(제어 전압 U UPR)를 갖는 마이크로파 발생기(VCO);

3 - 전자레인지 믹서;

4 - 마이크로파 입력 주파수가 있는 입력 마이크로파 신호 소스;

5 - 가변 분할비 n을 갖는 첫 번째 주파수 분배기;

6 - 주파수 위상 검출기(출력 전압 U PFD);

7 - 가변 분할비 m을 갖는 두 번째 주파수 분배기;

8 - 주파수 f OP를 갖는 기준 신호 소스;

9 - 연산 증폭기;

10 - 저역 통과 필터;

11 - 위상 비교기(출력 전압 U FC);

12 - 대기 멀티바이브레이터(직접 출력 전압 U m1 및 역수)

13 - 첫 번째 다이오드;

14 - 두 번째 다이오드;

f IF =f 마이크로파 입력 -f VCO - 중간 주파수 신호;

f MF - 마이크로파 주파수 합성기의 출력 신호.

그림에서. 그림 2는 제안된 마이크로파 주파수 합성기의 일부인 대기 멀티바이브레이터의 입력 U FC 및 출력 전압 U m1 및 U m2의 타이밍 다이어그램을 보여줍니다.

TM - 대기 중인 멀티바이브레이터(12)의 진동 주기;

τ m - 대기 중인 멀티바이브레이터(12)의 펄스 지속 시간;

τ PLL은 위상 고정 루프에서 동기화를 설정하는 시간입니다.

그림에서. 그림 3은 제안된 마이크로파 주파수 합성기의 고정 주파수 f 입력 마이크로파 입력 신호에 대한 주파수 fMF =fVCO인 출력 마이크로파 신호의 튜닝 대역폭을 보여줍니다.

그림에서. 그림 4는 제안된 마이크로파 주파수 합성기의 조정 가능한 주파수 f 입력 마이크로파 입력 신호에 대해 주파수 fMF =fVCO인 출력 마이크로파 신호의 튜닝 대역폭을 보여줍니다.

제안된 마이크로파 주파수 합성기의 블록 다이어그램은 그림 1에 나와 있습니다. 1에는 마이크로파 전압 제어 발생기(VCO) 1이 포함되어 있으며 그 출력은 방향성 커플러(2)의 입력에 연결되어 있으며 그 중 하나의 출력은 마이크로파 주파수 합성기의 출력이고 다른 하나는 방향성 커플러의 출력입니다. 2는 마이크로파 믹서(3)의 첫 번째 입력에 연결되고, 두 번째 입력은 주파수 f 마이크로파 입력을 갖는 입력 마이크로파 신호(4)의 출력 소스에 연결됩니다. 마이크로파 믹서(3)의 출력은 가변 분할 계수 n을 갖는 제1 주파수 분배기(5)의 입력에 연결되고, 그 출력은 주파수-위상 검출기(6)의 제1 입력에 연결된다. 위상 검출기(6)는 가변 분할 계수 m을 갖는 제2 주파수 분배기(7)의 출력에 연결되고, 입력은 주파수 fOP를 갖는 기준 신호원(8)의 출력에 연결된다. 주파수 위상 검출기(6)의 두 출력은 연산 증폭기(9)의 두 입력에 연결되며, 그 출력은 마이크로파 VCO 발생기(1)의 입력에 연결되고 저역 통과 필터(10)는 연산 증폭기(9)의 첫 번째 입력 사이에 연결됩니다. 연산 증폭기(9) 및 그 출력 회로(11)에 추가로 도입된 위상 비교기의 제1 입력은 제1 주파수 분주기(5)의 출력과 주파수-위상 검출기(6)의 제1 입력에 연결되고, 위상의 두 번째 입력은 비교기(11)는 제2 주파수 분배기(7)의 출력과 주파수-위상 검출기(6)의 제2 입력에 연결된다. 위상 비교기(11)의 출력은 대기 멀티바이브레이터(12)의 입력에 연결되고, 그 출력은 다음을 통해 지시된다. 제1 다이오드(13)는 주파수-위상 검출기의 제1 출력과 연산 증폭기(9)의 제1 입력에 연결되고, 제2 다이오드(14)를 통한 대기 멀티바이브레이터(12)의 역 출력은 주파수-위상 검출기의 제2 출력에 연결된다 도 6에 도시된 바와 같이 연산 증폭기(9)의 제2 입력에는 제1 다이오드와 제2 다이오드가 서로 반대 방향으로 연결된다. 이 회로에서는 마이크로파 VCO 1, 방향성 커플러 2, 마이크로파 믹서 3, 제1 주파수 분배기 5, 주파수 위상 검출기 6, 제2 주파수 분배기 7, 연산 증폭기 9 및 저역 통과 필터 10이 PLL 루프를 형성합니다.

제안된 마이크로파 주파수 합성기는 다음과 같이 동작한다. 커플러 2를 통해 주파수 f VCO를 갖는 마이크로파 VCO 1의 출력 신호와 주파수 f 입력 마이크로파를 갖는 입력 마이크로파 신호 소스 4의 출력 마이크로파 신호는 마이크로파 믹서 3에 공급되며, 그 출력에서 중간 주파수 f IF의 신호가 출력됩니다. 이는 제1 주파수 분배기(5)의 입력에 공급되고, n 인자로 나눈 후, 제1 주파수 분배기(5)의 출력으로부터의 신호는 주파수-위상 검출기(6)의 제1 입력에 공급된다. 기준 신호원(8)의 출력으로부터의 주파수 신호 fOP는 제2 주파수 분배기(7)의 입력에 공급되며, 여기서 주파수는 인자 m으로 나누어진다. 제2 주파수 분주기(7)의 출력으로부터의 신호는 주파수 위상 검출기(FPD)(6)의 제2 입력에 공급되어 제1 주파수 분주기(5)의 출력으로부터 수신된 신호와 비교되고, 전압 U FPD는 주파수-위상 검출기(6)의 두 출력에서 생성되며, 그 크기와 부호는 비교된 신호의 주파수와 위상의 차이에 비례합니다. 이 제어전압(U PFD )은 연산증폭기(9)의 피드백 회로에 포함된 연산증폭기(9)와 저역통과필터(10)를 거쳐 마이크로파 VCO(1)의 제어입력에 제어전압(U Ctrl)으로 공급되어 다음과 같은 동작을 수행한다. 마이크로파 VCO 1의 주파수를 지속적으로 조정하여 PLL 루프의 위상 모드 동기화에 영향을 미칩니다.

PLL 루프에서 주파수-위상 동기화를 수행하기 위한 조건은 주파수-위상 검출기의 입력에 공급되는 신호의 주파수와 위상이 동일해야 합니다. 즉, f OP /m=f IF /n, ψ OP = ∨ 만약에,

여기서 f IF = f 입력 마이크로파 -f VCO,

m은 기준 신호의 주파수를 주파수 f OP로 나눈 계수입니다.

n은 중간 주파수 신호 f IF의 주파수 분할 인자이고;

ψ OP - 주파수 f OP를 갖는 기준 신호의 위상;

ψ IF - 중간 주파수 신호 f IF의 위상.

마이크로파에서 입력 마이크로파 신호 f의 주파수가 중간 주파수 신호 f IF의 주파수의 두 배 이상인 대역에서 조정될 때(여기서 마이크로파에서 f IF = f -f VCO), 제안 발명의 마이크로파 신호 f VCO f VCO는 2f IF 이상 이동하며, 제안 발명의 입력 마이크로파 신호 f 입력 마이크로파는 마이크로파 주파수 합성기의 PLL 루프, 즉 위상 비교기(11), 대기 멀티바이브레이터(12)를 통과하고, 뿐만 아니라 백투백 다이오드(13, 14)도 포함된다.

PLL 루프에 위상 동기화가 있는 경우 위상 비교기(11)의 출력에서 대기 멀티바이브레이터(12)로 제어 신호가 수신되어 대기 멀티바이브레이터(12), 즉 위상 비교기(11)의 출력 전압(UFC)이 꺼진다. (예를 들어, 트랜지스터-트랜지스터 로직 TTL의 레벨)을 논리 단위 형태로 나타냅니다. 이때, 대기 중인 멀티바이브레이터(12)는 정 출력과 역 출력 각각에서 전압 U M1, U M2 의 펄스 출력 신호를 생성하지 않으며 PLL 루프의 동작에 영향을 미치지 않는다. 대기 멀티바이브레이터(12)의 정전압 및 역출력에서 정전압 U M1 및 U M2는 논리 0 및 논리 1에 대응하는 역위상으로 설정된다. 대기 멀티바이브레이터(12)의 입력 U FC 및 출력 전압 U M1 및 U M2의 타이밍 다이어그램이 도 1에 도시되어 있다. 2

PLL 루프의 주파수 및 위상 동기화가 방해받는 경우, 위상 비교기(11)의 출력에서 나온 논리 0 형태의 U FC 신호는 대기 멀티바이브레이터(12)를 트리거하며, 이는 직접 및 역 출력에서 다음과 같은 출력 펄스 신호를 생성합니다. 다이오드 13, 14를 통해 각각 연산 증폭기 9의 첫 번째 및 두 번째 입력에 도달하는 전압 U M1 (논리 장치에 해당) 및 U M2 (논리 0에 해당) 즉, PFD(6)의 입력 위상에 따라 대기 멀티바이브레이터(12)의 펄스 기간 τ m 동안 출력 연산 증폭기(9)에서 주파수에 대한 제어 전압의 최대 또는 최소값을 설정합니다. 이 경우, 주파수-위상 동기화 조건이 위반되고(f OP /m=f IF /n, ψ OP = ψ IF) 주파수-위상 검출기(6)는 제어 전압을 생성합니다. U PLL 루프에서 동기화 복원(즉, 동기화 프로세스의 시작)을 보장하는 PFD. PLL 루프에서 주파수-위상 동기화가 복원되면 위상 비교기(11)는 대기 멀티바이브레이터(12)를 끕니다(해당 출력에서 논리 0과 논리 1에 해당하는 정전압이 다시 역위상으로 설정됨). PLL 루프에서 주파수-위상 동기화가 반복적으로 위반되거나 PLL 루프의 오작동이 발생하는 경우 위상 비교기(11)는 대기 중인 멀티바이브레이터(12)를 다시 시작하고 동기화를 복원하는 전체 프로세스가 반복됩니다.

어떤 경우에는 PLL 루프의 작동을 위해 주파수-위상 동기화 위반을 제외하고 PLL 루프에서 마이크로파 VCO의 주파수를 조정하는 과도 프로세스가 낮은 것부터 시작해야 합니다(f VCO min ) 또는 f VCO = f MF인 주파수 캡처 지점까지의 마이크로파 VCO 작동 범위의 상위(f VCO max) 에지, 즉 마이크로파 VCO 1의 제어 입력에 공급되는 초기 전압 레벨(과도 상태에서) 주파수 캡처 이전 모드)는 항상 최소값 또는 최대값과 동일했습니다. 이는 마이크로파 입력 신호의 마이크로파 주파수 f에 대한 마이크로파 VCO 출력 신호의 VCO 주파수 f의 위치에 의해 결정됩니다. 이 경우 마이크로파 주파수 합성기의 두 가지 주요 작동 모드가 가능하며 이 모드에서 PLL 루프의 동기화가 중단될 수 있습니다.

그림 1에 표시된 마이크로파 주파수 합성기의 첫 번째 작동 모드를 고려해 보겠습니다. 3. 마이크로파 입력 신호의 주파수 f가 고정되어 fMF를 초과하고(프로토타입에서와 같이) 마이크로파 VCO 1의 튜닝 대역(ΔfVCO)이 충분히 크다고 가정합니다. 예를 들어 값을 크게 초과합니다. 2f IF. 이 경우, 주파수 캡처 이전의 과도 프로세스 동안 마이크로파 믹서(3)의 출력에서 나온 미러 주파수 신호는 주파수 위상 검출기(6)에 도달할 수 있습니다(동기화 실패 지점에서 f VCO = f 1 MF, 여기서 f 1 MF = f 입력 마이크로파 +f IF), 이로 인해 PLL 루프에서 동기화가 실패하고 마이크로파 VCO의 주파수 f VCO 신호가 주파수 f VCO max에 해당하는 최상위 위치로 전환됩니다. 결과적으로 마이크로파 주파수 합성기의 작동이 중단되었습니다. 프로토타입으로 선택된 마이크로파 주파수 합성기의 회로는 이러한 상황을 해결할 가능성을 제공하지 않습니다. 제안된 마이크로파 주파수 합성기에서는 이 문제를 다음과 같이 해결한다.

주파수-위상 동기화 모드(f OP /m=f IF /n, ψ OP = ψ IF)의 위상 비교기(11)는 논리 유닛(논리 "1")에 대응하는 출력에서 신호 U FC를 생성한다. 위상 비교기(11)의 이 출력은 논리 0(논리 "0")에 대응하는 신호에 의해 트리거되는 대기 멀티바이브레이터(12)의 입력에 연결된다. 입력 신호가 로그 레벨과 동일합니다. "0"이면 첫 번째 13개 및 두 번째 14개의 다이오드가 닫히고 대기 멀티바이브레이터(12)가 PLL 루프의 작동에 영향을 주지 않습니다. 위상동기화 모드를 위반한 경우, 위상비교기(11)의 출력에는 로그에 해당하는 신호가 나타난다. "0". 이는 마이크로파 주파수 합성기가 켜져 있거나 기준 신호의 주파수 f가 조정될 때 발생할 수 있습니다. 로그에 해당하는 신호입니다. 위상 비교기(11)의 출력에서 "0"은 대기 멀티바이브레이터(12)를 트리거하고 그 직접 및 역 출력에서 펄스 지속 시간 τ m 동안 전압 레벨은 각각 로그 "1" 및 로그와 동일하게 나타납니다. "0"(즉, 이전 상태와 반대)이므로 첫 번째 13개 및 두 번째 14개의 다이오드가 개방되고 연산 증폭기(9)의 첫 번째 및 두 번째 입력에 차동 전압이 공급되어 초기(최소) 마이크로파 VCO(1)의 주파수 제어 입력에 각각 공급되는 연산 증폭기(9)의 출력에서의 제어 전압은 마이크로파 VCO f VCO =f VCO min의 주파수 값을 설정한다. 대기 멀티바이브레이터(12)의 펄스가 끝난 후, T M -τ m 값과 동일한 일시 정지가 있으며, 여기서 T M은 대기 멀티바이브레이터(12)의 펄스 반복 주기이다. 이 일시 정지 동안 PLL 루프는 주파수 f VCO를 조정한다 마이크로파 VCO 신호의 최소값 f VCO min 에서 주파수 위상 동기화가 발생하는 주파수 까지(그림 3의 주파수 고정 지점). 마이크로파 VCO 신호의 주파수 f VCO가 f VCO =f MF(여기서 f MF =f 입력 마이크로파 -f IF)인 값으로 조정되고 f VCO ≤f 입력 마이크로파 조건에 따라(다음에 따라) PFD의 위상 조정 6), f OP /m=f IF /n인 주파수-위상 동기화 모드가 설정됩니다. 위상 비교기(11)의 출력에는 로그 레벨에 해당하는 신호가 나타납니다. "1", 멀티바이브레이터(12)를 대기 상태로 전환합니다. 어떤 이유로 동기화 프로세스가 발생하지 않으면 PLL 루프에서 동기화를 설정하는 설명된 주기가 반복됩니다. 이 경우 주파수 캡처에 필요한 조건은 대기 중인 멀티바이브레이터(12)의 펄스 반복 주기가 T M -τm>τ PLL 루프 조건을 충족해야 한다는 것입니다.

T M - 대기 중인 멀티바이브레이터의 펄스 반복 주기,

τ m - 대기 중인 멀티바이브레이터의 펄스 지속 시간,

τ PLL 루프 - PLL 루프에서 동기화를 설정하는 시간입니다.

그림 1에 표시된 마이크로파 주파수 합성기의 두 번째 작동 모드를 고려해 보겠습니다. 4.

마이크로파 주파수 합성기의 초기 순간에 f 입력 마이크로파 = f 입력 마이크로파1로 주파수-위상 동기화 조건이 만족된다고 가정해 보겠습니다. 이 경우, 마이크로파 주파수 합성기의 출력 신호의 주파수는 f MF =f MF·1 =f 입력 마이크로파1 -f IF이다. 그런 다음 마이크로파 입력 신호의 주파수 f는 입력 마이크로파 신호의 마이크로파 튜닝(그림 4 참조)에서 밴드 Δf에서 마이크로파1의 f 값에서 마이크로파2의 값 f(이 경우 주파수)로 빠르게 조정됩니다. 마이크로파에서 입력 마이크로파 신호 Δf의 튜닝 대역은 2f IF보다 큽니다. 여기서 f IF =f 입력 마이크로파 -f VCO 주파수 튜닝 f 입력 마이크로파와 동시에 f VCO 마이크로파 VCO의 주파수 튜닝은 f MF1 값에서 발생합니다. 그러나 PLL 루프의 관성으로 인해 입력의 주파수 튜닝 시간 마이크로파 신호(t AC 마이크로파 입력)는 항상 PLL 루프(τ PLL 루프)의 동기화 설정 시간보다 작습니다. 즉, t AC 마이크로파 입력 ≤τ PLL 루프입니다.

PLL 루프의 관성으로 인해 마이크로파 VCO의 주파수를 튜닝할 때 동기화가 중단되는 조건도 발생합니다. 예를 들어, 도 1에 도시된 바와 같이. 도 4를 참조하면, VCO의 주파수 f를 f MF1의 초기 값(마이크로파 VCO의 주파수 튜닝 범위의 상위 부분)에서 f MF2의 다음 낮은 주파수 값으로 조정할 때. 마이크로파 믹서에서는 f VCO = f 1 MF2 = fin 마이크로파 2 + f IF인 지점에서 거울 중간 주파수 신호가 형성됩니다. 이 경우(PFD 6의 특정 위상 사용) f VCO ≤f 마이크로파 입력 조건이 충족되지 않습니다. 즉, 주파수가 PLL 루프에 의해 캡처되지 않아 주파수-위상 동기화가 위반됩니다. 주파수 f VCO를 상한값 f VCO로 "드래깅" 마이크로파 VCO의 최대 주파수 튜닝 범위. 제안된 발명에서 PLL 루프의 주파수-위상 동기화를 복원하기 위해서는 마이크로파 주파수 합성기의 첫 번째 동작 모드에서 설명한 동기화 설정 사이클을 수행해야 한다. 프로토타입으로 선택된 마이크로파 주파수 합성기의 회로는 입력 마이크로파 신호의 주파수를 빠르게 변경할 수 있는 가능성을 제공하지 않으므로 이러한 회로는 입력 마이크로파의 주파수를 조정할 때 안정적인 위상 동기화를 허용하지 않습니다. 신호.

본 발명의 프로토타입으로 선택된 잘 알려진 마이크로파 주파수 합성기에서 PLL 시스템의 불안정한 작동에 대한 위에서 설명한 모드가 실험적으로 테스트되고 확인되었습니다.

제안된 발명을 기반으로 마이크로파 주파수 합성기의 샘플을 개발하고 실험적으로 테스트한 결과, 마이크로파 주파수 합성기의 다양한 작동 모드에서 주파수-위상 동기화의 빠른 복구 시간(100μs 미만)으로 안정적인 작동이 확인되었습니다.

정보 출처

1. Manasevich V. 주파수 합성기. 이론과 디자인. - M.: 커뮤니케이션, 1979

2. Ryzhkov A.V., Popov V.N. 무선 통신 기술의 주파수 합성기. - M.: 라디오 및 통신, 1991, p. 110-113.

전압 제어 마이크로파 발진기(VCO)를 포함하는 마이크로파 주파수 합성기로서, 그 출력은 방향성 결합기의 입력에 연결되고, 첫 번째 출력은 마이크로파 주파수 합성기의 출력이고, 두 번째 출력은 방향성 커플러의 입력이다. 커플러는 마이크로파 믹서의 첫 번째 입력에 연결되고, 마이크로파 믹서의 두 번째 입력은 입력 마이크로파 신호의 출력 소스에 연결되고, 마이크로파 믹서의 출력은 변수가 있는 첫 번째 주파수 분배기의 입력에 연결됩니다. 분할비는 출력이 주파수-위상 검출기의 제1 입력에 연결되고, 주파수-위상 검출기의 제2 입력은 가변 분할비를 갖는 제2 주파수 분할기의 출력에 연결되며, 그 입력은 다음과 같습니다. 기준 신호 소스의 출력과 연결되고, 주파수-위상 검출기와 마이크로파 VCO 사이에는 저역 통과 필터가 포함되며, 마이크로파 주파수 합성기는 위상 비교기, 대기 멀티바이브레이터, 두 개의 다이오드 및 주파수 위상 검출기의 첫 번째 및 두 번째 출력이 연산 증폭기의 첫 번째 및 두 번째 입력에 각각 연결되는 연산 증폭기, 그 출력은 마이크로파 VCO의 입력에 연결되고 저역 통과 필터는 다음과 같습니다. 연산 증폭기의 첫 번째 입력과 그 출력 사이에 연결되고, 위상 비교기의 첫 번째 입력은 가변 분배 계수를 가진 첫 번째 주파수 분배기와 첫 번째 입력 주파수-위상 검출기의 출력에 연결되고, 위상의 두 번째 입력은 비교기는 가변 분할 계수를 갖는 두 번째 주파수 분배기의 출력에 연결되고 주파수-위상 검출기의 두 번째 입력에는 위상 비교기의 출력은 대기 멀티바이브레이터의 입력에 연결되고 대기의 첫 번째 출력은 멀티바이브레이터는 첫 번째 다이오드를 통해 주파수-위상 검출기의 첫 번째 출력에 연결되고 위상 검출기는 연산 증폭기의 첫 번째 입력과 대기 멀티바이브레이터의 두 번째 출력은 두 번째 다이오드를 통해 주파수의 두 번째 출력에 연결됩니다. - 위상검출기와 연산증폭기의 제2입력으로, 제1,2다이오드는 서로 반대방향으로 연결되며, 마이크로파 VCO, 방향성 결합기, 마이크로파 믹서, 제1주파수분할기, 주파수-위상검출기, 연산 증폭기와 저역 통과 필터는 다음 조건에서 위상 고정 루프(PLL)를 형성합니다. T M -τ m >τ PLL, 여기서 T M은 대기 중인 멀티바이브레이터의 발진 주기이고, τ m은 대기 중인 멀티바이브레이터의 지속 시간 펄스입니다. τ PLL은 위상 고정 루프에서 동기화를 설정하는 시간입니다.

유사한 특허:

본 발명은 통신기술에 관한 것이다. 기술적 결과는 동기화 시스템의 주요 매개변수의 포괄적인 개선, 즉 잡음 내성 증가, 시스템의 필터링 속성 개선, 획득 대역 확장 및 동기 작동 모드 유지, 동기 작동 진입 시간 단축으로 구성됩니다. 모드에서는 정적 위상 오류가 발생하지 않도록 보장하고 입력 신호 진폭의 변화 및 변동 또는 위상 검출기의 전송 계수 변화가 있는 경우 장치의 올바른 작동을 보장합니다.

본 발명은 무선 신호의 주파수 선택 및 필터링에 관한 것이다. 기술적 결과는 무선 신호 선택 장치를 간섭 조건에 적응시키고 에너지 소비를 제어하는 기능을 보장하는 것입니다.

전환된 주파수 감소 경로를 갖춘 주파수 합성기는 무선 엔지니어링과 관련이 있으며 잡음 내성이 향상된 수신 장치는 물론 작동 주파수를 빠르게 조정하는 트랜시버 장치에서 균일한 단계로 안정적인 주파수 그리드를 형성하는 데 사용할 수 있습니다.

제안된 방법은 통신 기술 및 제어 발진기(CG)를 포함하는 동기화 장치(BS)의 작동 모드, 보다 정확하게는 홀드 모드에서 BS CG의 매우 안정적인 출력 신호를 생성하는 방법에 관한 것입니다.

본 발명은 전자 장비, 즉 분수 잡음 보상 기능을 갖춘 펄스 위상 고정 루프(PLL) 기반의 주파수 그리드 합성기(GSS)에 관한 것이며 보상 전류의 진폭 또는 펄스 폭 변조에 기반한 방식을 사용할 때 사용될 수 있습니다.

본 발명은 무선 공학 및 자동화 분야에 관한 것으로, 향상된 안정화 특성을 지닌 연속 가스 레이저의 방사선 주파수를 자동으로 조정하는 시스템에 관한 것이며, 특히 주파수의 "보라색 이동"을 측정하기 위해 우주 기술에 사용될 수 있습니다. 지구 중력장의 레이저 방사선.

본 발명은 전자 컴퓨터 기술 및 무선 공학에 관한 것입니다. 기술적 결과는 다중 주파수 주파수 변조 신호를 생성하는 속도와 능력을 높이는 것입니다. 주파수 변조 신호의 디지털 전산 합성기에는 기준 생성기, 성형 및 지연 장치, 3개의 메모리 레지스터, 4개의 디지털 드라이브, 가변 분할 비율이 있는 분배기, 2개의 기능 변환기 코드 x - sin x, 2개의 역 필터 sin이 포함됩니다. x/x, 정류자, 디지털-아날로그 변환기 2개. FM DAC 신호의 디지털 입력은 첫 번째, 두 번째 및 세 번째 메모리 레지스터의 입력이고, 아날로그 출력은 첫 번째 및 두 번째 DAC의 출력입니다. 2 병.

본 발명은 무선공학 분야에 관한 것이다. 기술적인 결과는 부호 있는 논리위상판별기의 판별특성의 대칭형상을 비대칭형으로 변경하고, 판별특성의 양 또는 음의 부호의 면적을 증가시켜 캡쳐밴드를 확장한 것이며, 해당 부호의 초기 주파수 디튜닝에 대한 해당 일방적 캡처 대역이 증가합니다. 상기 판별기를 이용한 위상동기루프 시스템의 캡쳐 대역폭을 증가시키는 방법은 제어되는 발전기에서 발생하는 입력 발진과 출력 발진의 차이의 부호를 결정하고, 제어되는 발생기의 주파수를 제어하는 단일 신호로 결합되는 위상차. 2n.p. f-ly, 7병.

위상 고정 루프 방법을 사용하면 잡음이 있는 단상 소스 신호로부터 동기화할 수 있습니다. 기술적 결과는 동기화된 주파수 신호의 1개 또는 2개 주기로 실제 동기화 속도를 향상시키고, 생성된 동기화된 위상 및 주파수 신호의 간섭을 필터링하는 것으로 구성됩니다. 시스템은 1차 위상 필터링 블록, 2차 대역 저지 필터, 1차 저주파 필터링, 적분 블록, 곱셈 블록, 디지털 필터 계수 계산용 블록 및 4사분면 아크탄젠트 블록을 포함합니다. . 마이크로프로세서 수단을 사용하여 방법을 물리적으로 구현하기 위해 이산 방법을 사용하면 허용 가능한 정확도와 컴퓨팅 리소스를 사용하여 비선형 함수의 비교 작업 및 계산이 가능합니다. 필터는 가변 계수로 구현되며 1차 및 2차를 갖습니다. 주파수 변화에 대한 위상 필터의 민감도가 상대적으로 낮기 때문에 원래 신호에서 기준 위상을 신속하게 추출할 수 있습니다. 적분 계수에 대한 피드백이 있는 이산 적분기를 사용하면 동기화된 주파수 신호가 빠르게 정상 상태에 도달할 수 있습니다. 가변 계수가 있는 이산 필터를 사용하고 경계 값을 통한 위상 전이를 고려하면 원래 신호의 기본 고조파 위상을 기준으로 이동하지 않고 동기화된 위상을 효과적으로 필터링할 수 있습니다. 이 방법을 사용하면 단상 및 다상 시스템의 고조파 구성 요소와 다상 시스템의 대칭 구성 요소를 기반으로 하는 기본 제어 시스템을 구축할 수 있습니다. 이 방법의 주요 응용 분야는 변환기 장비를 제어하는 것입니다. 기본 주파수로 조정하고 기준 위상을 분리하기 위한 고성능 요구 사항이 있는 통신 및 기타 응용 분야에서 빠른 동기화에도 사용할 수 있습니다. 1 병.

본 발명은 무선 공학 분야에 관한 것이며 작은 단계의 주파수 튜닝이 필요한 측정 기술뿐만 아니라 채널 수가 증가한 통신 시스템을 구성하는 데 사용될 수 있습니다. 본 발명의 기본은 작은 주파수 그리드 단계, 낮은 수준의 위상 잡음 및 짧은 주파수 튜닝 시간으로 마이크로파 진동을 얻는 작업입니다. 이를 위해 간접형 합성기의 위상 검출기에서 비교 주파수를 설정하는 기준 발진기의 주파수를 초단파 대역에서 선택한다. 이 경우, 매우 안정적인 기준 발진기의 주파수는 먼저 특정 작은 양만큼 이동되어 주파수 그리드의 작은 단계를 설정합니다. 이를 위해 기준 발진기의 신호는 직교 변조기의 무선 주파수 입력으로 공급되며, 주파수와 진폭은 동일하지만 위상 변이가 90°인 저주파 직교 신호로 변조됩니다. 그런 다음 비교 주파수는 이러한 저주파 신호의 주파수 값만큼 기준 발진기의 주파수와 다릅니다. 직교 변조기의 출력에서 주파수 변환된 신호는 주파수 위상 검출기의 첫 번째 입력으로 공급됩니다. 전압 제어 마이크로파 발생기의 주파수는 가변 계수가 있는 분배기로 나누어지고 주파수-위상 검출기의 두 번째 입력으로 공급됩니다. 저역 통과 필터를 사용하면 AC 기준 제품이 억제되고 DC 신호가 전압 제어 마이크로파 발진기의 입력으로 공급됩니다. 이 방법을 사용하면 합성기의 튜닝 시간을 늘리지 않고 위상 잡음 수준을 높이지 않고 기준 발진기 주파수의 안정성에 따라 결정되는 합성기 주파수의 안정성을 유지하지 않고도 수 킬로헤르츠 단위로 마이크로파 발진을 형성할 수 있습니다. 예를 들어 10-7-10-8에 도달합니다.

본 발명은 무선 전자 장치, 특히 위상 고정 루프(PLL)를 기반으로 하는 주파수 합성기에 관한 것입니다. 기술적 결과는 출력 신호 스펙트럼의 위상 잡음 및 스퓨리어스 개별 구성 요소 수준을 줄여 결과적으로 출력 신호의 품질을 향상시키는 동시에 고주파수 분해능과 넓은 튜닝 대역을 유지하는 것으로 구성됩니다. 주파수 합성기에는 직렬 연결된 입력 신호 주파수 체배기, 고정 분배 계수가 있는 분배기, 첫 번째 직접 디지털 합성 마이크로 회로, 위상 주파수 감지기, 첫 번째 저역 통과 필터, 전압 제어 발생기, 네거티브 피드백이 포함되어 있습니다. 직렬 연결된 믹서, 입력 중 하나는 전압 제어 발생기의 출력에 연결되고 두 번째 입력은 입력 신호 주파수 체배기의 출력에 연결되고 두 번째 저역 통과 필터와 두 번째 입력을 포함하는 회로 출력이 위상 주파수 검출기의 입력에 연결된 직접 디지털 합성 마이크로 회로와 출력이 첫 번째와 두 번째의 입력에 연결된 제어 장치는 직접 디지털 합성 칩입니다. 본 발명은 출력 신호 스펙트럼의 위상 잡음 및 이산 성분의 수준을 감소시키며, 이는 결과적으로 높은 주파수 분해능과 넓은 튜닝 대역을 유지하면서 출력 신호의 품질을 향상시킵니다. 1 병.

본 발명은 무선공학에 관한 것이다. 본 발명의 기술적 결과는 주기가 클록 주기의 배수인 모든 듀티 사이클의 기준 신호로 작업할 수 있는 속도와 기능을 향상시키고 가장자리를 따라 클록 주파수를 조정하는 기능을 제공하는 것입니다. 수신된 데이터의 펄스 지속 시간 동안 위상 검출기(PD)의 출력에서 양극 및 음극 신호가 생성된 후 합산, 필터링되고 결과 신호가 발생기의 주파수를 제어하는 주파수 조정 방법입니다. , 첫 번째 출력의 펄스 에지는 기준 신호의 에지를 따르고 클럭 전환에 대한 컷오프를 따릅니다. 기준 신호의 에지가 클록 사이클의 에지보다 늦게 나타나면 클록 일시 정지 기간 동안 PD의 두 번째 출력에서도 신호가 생성됩니다. FD에는 3개의 2-I 소자, 3개의 D-플립플롭 및 3개의 신호를 연결하기 위한 논리 회로가 포함되어 있습니다. 2엔. 그리고 월급 7 f-ly, 11병.

본 발명은 레이더 및 소나에 관한 것이다. 기술적 결과는 홀수 길이의 P3 코드에 대해 사이드 로브를 억제하는 것입니다. 이를 위해 다상 P3 코드의 펄스 압축 중에 사이드 로브를 억제하는 장치에는 입력에 연결된 홀수 길이 N의 P3 코드에 대한 수정된 Woo 필터와 직렬 연결된 코드 변환기의 디지털 보정 신호 생성기가 포함되어 있습니다. 켤레 코드 및 (N+2) 계수 -1.1, 0,…0, -1.1, 첫 번째 입력에 연결된 덧셈기의 출력, 지연을 갖는 FIR 필터 N+1 차수의 유한 임펄스 응답을 갖는 디지털 필터 하나의 코드 요소와 두 개의 입력 감산기 동안의 라인. 여기서 Woo 필터의 출력은 입력 지연 라인에 연결되고 감산기의 첫 번째 입력에 연결되고 출력은 가산기의 두 번째 입력에 연결됩니다. 감산기의 두 번째 입력은 지연선의 출력에 연결되고, 수정된 필터 Woo의 첫 번째 임펄스 응답 계수는 1 - exp(iπ/N)과 같습니다. 여기서, (N+2) 차원 벡터 디지털 보정 신호 형성기의 필터 계수는 각각 -1.1, 0.0,…0, -1.1과 같습니다. 2 병.

제안된 장치는 다단계 코드의 펄스 압축을 사용하는 레이더 및 소나 시스템과 관련됩니다. 기술적인 결과는 신호 압축의 품질을 향상시키는 것으로 구성됩니다. 압축 과정에서 발생하는 사이드 로브가 억제되어 다음을 제외한 모든 시간 이동(샘플) 값에 대해 길이 N의 다중 위상 코드 수의 증가가 보장됩니다. 두 개의 ±N, 여기서 사이드 로브의 상대 레벨은 첫 번째와 마지막의 동일한 수를 순차적으로 제거하여 형성된 대칭적으로 잘린 코드를 사용하기 때문에 -20 logN -6 ~ -20 logN -8 dB 범위에 있습니다. 더 긴 코드의 기호. 이 경우 -6dB 레벨에서 메인 로브의 폭은 2τ이고, PSL 레벨에서는 3~4τ 범위이며, 장치 출력의 신호/잡음 손실은 -1.7dB입니다. 길이 N의 대칭적으로 절단된 다상 코드의 펄스 압축 중 사이드 로브를 억제하는 장치는 입력에 연결된 FIR 차 N-1의 첫 번째 디지털 필터와 복소수로 직렬 연결된 코드 변환기로 구성된 디지털 보정 신호 생성기를 포함합니다. 켤레 코드와 유한 임펄스 응답 차수 N+1의 두 번째 디지털 필터로 구성되며, 그 출력은 가산기의 첫 번째 입력에 연결되고, 첫 번째 디지털 필터의 출력은 1시간 동안 지연선에 연결됩니다. 코드 요소와 감산기의 첫 번째 입력에 연결되며 두 번째 입력은 지연선의 출력에 연결되고 출력은 가산기의 두 번째 입력에 연결됩니다. 3n.p. f-ly, 4 병.

이 발명품 그룹은 저장 장치에 관한 것이며 조정되지 않은 아키텍처에서 저장 장치에 쓰기 위한 타이밍을 제어하는 데 사용될 수 있습니다. 기술적 결과는 실제 클록 신호 분배 네트워크의 지연 변화에 대한 보상입니다. 이 장치에는 수신기 회로와 링 발진기 회로가 포함되어 있습니다. 수신기 회로에는 조정되지 않은 구성의 데이터 경로와 클록 분배 네트워크가 포함되어 있습니다. 링 발진기 회로에는 실제 클록 분배 네트워크와 일치하는 클록 분배 네트워크의 복제본이 포함되어 있습니다. 3엔. 그리고 월급 17 f-ly, 10 병.

시간 규모 생성기는 주파수, 위상 변이 및 시간 규모에 따라 신호를 동기화하는 장치를 의미합니다. 기술적 결과는 시간 규모 동기화의 정확성을 높이는 것입니다. 시간 척도 생성기에는 시간 척도 수신 블록, 내부 양자 시퀀스 생성기, 분배기, 시간 척도 전송 블록, 보호 간격 형성기, 시간 선택기, 전환 가능한 지연 라인 블록, 비교기 블록 및 선형으로 포함됩니다. 가변 전압 발생기. 5 병, 1 탭.

본 발명은 무선 공학에 관한 것이며 마이크로파 주파수 범위의 장치를 송신 및 수신하는 데 사용될 수 있습니다. 기술적인 결과는 입력되는 마이크로파 신호의 주파수를 튜닝할 때 안정적인 동작을 높이는 것입니다. 마이크로파 주파수 합성기는 전압 제어 마이크로파 발생기, 방향성 결합기, 마이크로파 믹서, 입력 마이크로파 신호 소스, 가변 분할 계수가 있는 첫 번째 주파수 분배기, 주파수 위상 검출기, 두 번째 주파수 분배기를 포함합니다. 가변 분배 계수, 기준 신호 소스, 저역 통과 필터, 위상 비교기, 대기 멀티바이브레이터, 다이오드 2개 및 연산 증폭기. 4 병.

저자: Alexander Chenakin(위상 매트릭스); 영어 번역 피박 A.V. 박사.발행일: 2007년 5월 1일

주파수 합성: 현재 솔루션 및 새로운 트렌드

주요특징

주파수 합성기는 거의 모든 통신, 측정 및 제어 시스템의 핵심 요소입니다. 다음은 차세대 마이크로파 주파수 합성기를 설계하기 위한 주요 요구 사항입니다.

주파수 범위 및 분해능 . 고정 또는 비교적 협대역(10-20%) 신호는 많은 응용 분야에서 충분할 수 있습니다. 그러나 최신 디지털 광대역 시스템은 여러 옥타브에 걸쳐 확장되는 훨씬 더 넓은 주파수 범위를 요구합니다. 넓은 주파수 대역폭과 높은 분해능(1Hz 이하)은 실험실 주파수 발생기, 스펙트럼 분석기 등 측정 장비의 필수 요구 사항입니다. 많은 응용 분야에서 사용할 수 있는 범용 광범위 솔루션을 개발하는 것이 적절해 보입니다.

출력 파워. 필요한 출력 전력 수준은 특정 애플리케이션에 따라 크게 달라질 수 있습니다. 일반적인 시나리오는 다양한 주파수 변환 시스템에서 신디사이저를 믹서 기준 소스로 사용하는 것입니다. 일반적으로 10~17dBm이 허용 가능한 수준이지만 일부 회로에서는 더 높은 전력이 필요합니다.

비고조파 왜곡. 비고조파 스펙트럼 성분( 박차를 가하다) - 개별 이산 주파수에서 합성기에 의해 생성된 원치 않는 주파수 제품입니다. 이러한 구성 요소의 위치와 수준은 특정 신디사이저의 구성 아키텍처와 주파수 계획에 따라 결정됩니다. 마이크로파 통신 시스템에서 비고조파 왜곡은 수신 장치가 수신된 신호를 분리하고 추가로 처리하는 능력을 제한할 수 있습니다. 따라서 합성기의 비고조파 스펙트럼 구성 요소 레벨은 최소화되고 일반적으로 주 신호 레벨에 비해 -60dBn을 초과하지 않지만 경우에 따라 -80dBn 이하로 줄여야 합니다. . 이를 위해서는 주파수 합성기 설계에 약간의 노력이 필요하며 일반적으로 다른 매개변수, 특히 위상 잡음 수준, 주파수 분해능 및 튜닝 속도 간의 절충안이 필요합니다.

위상 잡음 및 안정성 - 수신 시스템의 감도를 궁극적으로 제한하는 주요 매개변수 중 하나입니다. 합성기 안정성과 위상 잡음은 기준 신호( 참조), 신디사이저의 특정 아키텍처도 마찬가지입니다. PLL(위상 고정 루프) 사용을 기반으로 하는 합성기는 사용되는 조정 가능한 발진기에 따라 달라지며, 기본 주파수에서 큰 오프셋을 얻을 때 해당 잡음은 참조 신호의 유효 잡음보다 낮을 수 있습니다. 좋은 예는 YIG 생성기( YIG발진기), 소음 수준은 2~10GHz 이상의 주파수 범위에서 -120 ~ -130dBc/Hz(100kHz 디튜닝)에 도달할 수 있습니다.

조정 속도 신디사이저가 한 주파수에서 다른 주파수로 얼마나 빨리 튜닝될 수 있는지를 결정합니다. 튜닝에 필요한 시간은 일반적으로 신호 처리에 사용할 수 없기 때문에 중요한 매개변수입니다. 차세대 통신 시스템에서는 효과적인 처리량을 늘리기 위해 점점 더 높은 스위칭 속도가 필요합니다. 전통적으로 "느린" 측정 장비라도 튜닝 속도를 높여야 합니다. 전형적인 예는 4개의 독립적인 고속 주파수 합성기를 포함하는 새로운 벡터 네트워크 분석기입니다. 따라서 주파수 합성기 설계자는 이러한 추세를 고려해야 합니다. 필요한 튜닝 속도는 마이크로초 범위에 있습니다.

에너지 소비 및 크기. 현대 장비는 소형화되고 에너지 소비도 줄어드는 경향이 있습니다. 새로운 설계에서는 통합 수준이 높고 전력 소비가 낮은 칩을 사용해야 합니다. 또한, 부피가 크고 에너지 집약적인 YIG 생성기와 필터 사용을 중단해야 합니다.

특별 요구 사항

현대의 마이크로파 주파수 합성기는 기술적 특성의 지속적인 개선, 기능 확장, 크기 감소, 에너지 소비 및 최종 비용을 요구합니다. 그러나 특별한 요구 사항은 튜닝 속도를 높이는 것인데, 이는 현대 마이크로파 시스템의 처리량의 지속적인 확장에 따라 결정됩니다. 기존 계측 및 통신 시스템은 여전히 밀리초 범위에서 작동하지만 새로운 시스템은 필수 특성(위상 잡음, 고조파 왜곡)을 유지하면서 마이크로초 스위칭 속도가 필요하므로 이는 심각한 기술적 과제를 야기합니다. 또 다른 문제는 최종 비용을 줄이는 것이 상당히 "표준적인" 요구 사항임에도 불구하고 필요한 기술 솔루션의 선택 범위가 급격히 좁아진다는 것입니다.

마이크로초 범위의 튜닝 속도(낮은 잡음 및 왜곡과 함께!) 및 저렴한 비용과 같은 특별한 요구 사항은 차세대 주파수 합성기 개발의 핵심 매개변수가 될 가능성이 높습니다.

건축 솔루션

아래에서는 주파수 합성기의 다양한 아키텍처와 설계 기능에 대해 설명합니다. 튜닝 속도를 높이고 신디사이저 비용을 낮추는 것을 목표로 하는 기술 솔루션에 특히 주의를 기울입니다.

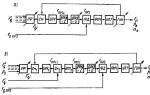

아날로그 신디사이저. 모든 신시사이저의 주요 기능은 참조 신호( 참조)을 필요한 출력 신호 수로 늘립니다. 아날로그 신디사이저( 직접비슷한 물건신디사이저)는 그림 1에 표시된 것처럼 개별 기본 주파수와 후속 필터링을 혼합하여 구현됩니다. 1. 기본 주파수는 저주파(석영, 계면활성제) 또는 고주파(유전체, 사파이어, 도파관, 세라믹 공진기) 발진기를 기반으로 곱셈, 나눗셈 또는 위상 고정 루프를 통해 얻을 수 있습니다.

이 토폴로지의 가장 큰 단점은 제한된 범위와 주파수 분해능입니다. 우리의 예(그림 1)에서는 18개 이하의 출력 주파수가 생성됩니다(믹서의 양쪽 측파대를 사용하더라도). 생성된 신호의 수는 그림 1에 표시된 것처럼 더 많은 기본 주파수 및/또는 혼합 단계를 도입하여 증가할 수 있습니다. 2. 그러나 이로 인해 사용되는 구성 요소 수가 급격히 증가하고 결과적으로 시스템이 복잡해집니다.

효과적인 해결책은 디지털( DDS) 합성기(그림 3)는 아날로그 부분에서 요구되는 최소 주파수 단계를 증가시킵니다.

|

또 다른 심각한 문제는 신중하게 필터링해야 하는 혼합 단계의 원치 않는 변환 생성물이 많다는 것입니다. 스위치 필터의 필수 절연을 보장하는 데 특별한 주의를 기울여야 합니다. 다양한 믹서 및 필터 설계가 알려져 있지만 일반적으로 작은 단계 크기와 넓은 주파수 적용 범위를 달성하려면 하드웨어(즉, 구성 요소)를 집중적으로 사용해야 합니다. 따라서 이 접근 방식은 예외적으로 빠른 튜닝 속도와 낮은 소음을 제공하지만 다소 높은 비용 특성으로 인해 사용이 제한됩니다.

디지털 신디사이저. 기존 솔루션과 달리 디지털 신디사이저( DDS-다이렉트 디지털 신디사이저) 디지털 처리를 사용하여 기본(클럭) 신호에서 원하는 출력 파형을 구성합니다. 위상 누산기를 사용하여 신호의 디지털 표현이 먼저 생성된 다음(그림 4), 그런 다음 디지털-아날로그 변환기(DAC - DAC). 디지털 신호 생성 속도는 주로 디지털 인터페이스에 의해 제한되며 아날로그 회로에 비해 상당히 높습니다. 디지털 신시사이저는 또한 상당히 낮은 위상 노이즈를 제공하며 심지어 사용된 클록 신호의 노이즈 감소도 입증합니다. 이러한 관점에서 디지털 신디사이저는 일반 주파수 분배기처럼 기능합니다. 그러나 디지털 신시사이저의 가장 큰 장점은 위상 배터리의 길이에 따라 결정되는 매우 높은 주파수 분해능(1Hz 미만)입니다.

|

주요 단점은 제한된 주파수 범위와 큰 신호 왜곡입니다. 디지털 신시사이저의 작동 주파수 범위의 하한은 실제로 DC 영역에 있지만 Nyquist 기준에 따르면 상한은 클록 주파수의 절반을 초과할 수 없습니다. 또한 출력 신호를 재구성하려면 저역 통과 필터를 사용해야 하며 출력 신호 범위를 클록 주파수의 약 40%로 제한합니다.

또 다른 심각한 문제는 바람직하지 않은 스펙트럼 생성물의 함량이 높다는 것입니다( 박차를 가하다) 양자화 및 DAC 변환 오류로 인해 발생합니다. 이러한 관점에서 볼 때 디지털 신디사이저는 주파수 믹서처럼 작동하여 조합 주파수에서 이산 제품을 생성합니다. 이러한 제품의 주파수 위치는 쉽게 계산할 수 있지만 진폭은 예측하기가 훨씬 어렵습니다. 일반적으로 낮은 차수의 제품은 가장 높은 진폭을 갖지만 특정 합성기의 주파수 계획을 설계할 때는 상당히 높은 차수의 제품을 고려해야 합니다. 또한 클록 주파수가 증가하면 진폭도 증가하는데, 이는 생성된 주파수 범위에 대한 추가 제한입니다. 범위 상한의 실제 값은 이산 스펙트럼 곱 -50...-60dBc 수준에서 수십 ~ 수백 MHz 범위에 있습니다. 분명히, 주파수 합성기 출력 신호의 직접적인 곱셈은 스펙트럼 구성의 추가 저하로 인해 실현될 수 없습니다.

디지털 신디사이저의 스펙트럼 구성을 개선하는 것을 목표로 하는 수많은 하드웨어 및 소프트웨어 솔루션이 있습니다. 하드웨어 방법은 일반적으로 디지털 신시사이저 신호의 주파수를 위로 이동시킨 후 그림 1과 같이 나누는 방식을 기반으로 합니다. 5. 이 방법은 주파수 분할 프로세스에 내재된 원치 않는 20dB/옥타브 스펙트럼 곱을 효과적으로 줄입니다. 불행하게도 이는 생성된 신호의 대역폭도 감소하므로 아날로그 회로와 유사하게 사용되는 기본 주파수 및 필터(그림 6)의 수를 늘려야 합니다.

소프트웨어 방법은 디지털 신디사이저의 개별 제품 위치가 출력 신호 및 클록 주파수(주파수 믹서와 유사)의 함수라는 사실을 기반으로 신디사이저의 주파수 계획을 최적화하는 것을 목표로 합니다. 따라서 주어진 출력 주파수에 대해 디지털 합성기의 클록 주파수를 변경하여 이산 제품의 주파수를 이동(따라서 필터링)할 수 있습니다. 이 기술은 클록 생성과 출력 신호의 협대역 필터링을 제공하는 PLL 시스템에서 특히 효과적으로 사용될 수 있습니다. 소프트웨어 방법은 상대적으로 작은 주문의 제품을 억제하는 데 매우 효과적으로 작동한다는 점에 유의해야 합니다. 불행하게도 이산 스펙트럼 곱의 밀도는 일반적으로 차수에 비례하여 증가하므로 이 방법의 실제 사용은 -70...-80dBn 수준으로 제한됩니다.

|

따라서 제한된 주파수 범위와 원치 않는 스펙트럼 제품의 함량이 높기 때문에 디지털 신시사이저는 마이크로파 신호를 직접 생성하는 데 거의 사용되지 않습니다. 동시에 고주파 분해능을 제공하기 위해 보다 복잡한 아날로그 및 PLL 시스템에 널리 사용됩니다.

PLL 신디사이저

위상 고정 루프를 사용하는 합성기는 일반적으로 아날로그 회로에 비해 크기와 복잡성 수준이 훨씬 작습니다. 따라서 일반적인 단일 루프 PLL 합성기는 조정 가능한 전압 제어 발진기(VCO - VCO), 필요한 (프로그래밍 가능한) 주파수 분할 후 신호는 그림 1에 표시된 것처럼 위상 검출기의 입력으로 전달됩니다. 7.

|

위상 검출기의 다른 입력은 기준 신호 소스에 연결됩니다( 참조), 그 주파수는 필요한 주파수 단계와 같습니다. 위상 검출기는 두 입력의 신호를 비교하고 (필요한 경우) 필터링 및 증폭 후 VCO 주파수를 f=F REF × N으로 조정하는 오류 신호를 생성합니다. 여기서 F REF는 참조 신호의 주파수입니다. 위상 검출기 입력.

PLL 기반 회로의 주요 장점은 저역 통과 필터(LPF - LPF),아날로그 신디사이저에 비해 복잡성 수준이 훨씬 낮습니다. 가장 큰 단점은 튜닝 시간이 길고(PLL 필터 대역폭과 주파수 단계에 반비례) 아날로그 회로에 비해 위상 잡음이 상당히 높다는 점입니다. PLL 필터 대역폭 내에서 합성기의 위상 잡음은 다음과 같습니다. PD+ 20 로그 N여기서 λPD는 기준 신호, 위상 검출기, 주파수 분배기, 필터 및 피드백 회로 증폭기의 전체 위상 잡음 레벨이며 위상 검출기의 입력으로 다시 계산됩니다(그림 8). 따라서 위상 잡음은 주파수 분배기의 분할 비율에 따라 달라지며 필요한 주파수 분해능을 제공하기에는 상당히 클 수 있습니다. 따라서 1MHz의 분해능으로 10GHz의 주파수에서 신호를 얻으려면 분할 계수가 10000과 같아야 하며 이는 80dB의 위상 잡음 증가에 해당합니다. 또한 프로그래밍 가능한 분배기는 상대적으로 낮은 주파수에서 사용되므로 고정된 분배 비율을 가진 추가 고주파 분배기가 필요합니다. (프리스케일러).이로 인해 피드백 루프의 전체 분할 비율이 증가하고 결과적으로 위상 잡음이 더욱 저하됩니다. 분명히 이러한 간단한 회로에서는 최신 저잡음 기준 신호 발생기의 잡음 기능을 사용할 수 없습니다. 또한 합성기 출력 스펙트럼에서 기준 신호의 고조파 성분은 일반적으로 피드백 분할 비율에도 비례합니다. 결과적으로 단일 루프 PLL 회로는 생성된 신호의 품질에 대한 높은 요구 사항을 두지 않는 시스템에서 제한적으로 사용됩니다.

|

그림 1과 같이 피드백 회로에 주파수 변환(믹서)을 도입하면 합성기의 기본 특성을 크게 향상시킬 수 있습니다. 9. 이 경우 VCO 신호는 주파수가 하향 전송되므로 피드백 회로의 분할 비율을 크게 줄일 수 있습니다. 믹서 기준 신호는 추가 PLL(다중 루프 루프) 또는 주파수 체배기를 사용하여 생성됩니다. 좋은 해결책은 내장 다이오드에 의해 생성된 기준 신호의 다중 고조파를 사용하는 고조파 믹서를 사용하는 것입니다. 하모닉 믹서를 사용하면 신디사이저 설계를 대폭 단순화할 수 있습니다. 동시에 이러한 유형의 믹서는 개별 회로 요소의 매개변수에 매우 민감하며 최적화가 결코 쉬운 작업이 아니라는 점에 유의해야 합니다.

|

위상 잡음 및 주파수 분해능에 대한 특정 요구 사항에 따라 더 많은 수의 믹싱 단계를 도입할 수 있지만 이로 인해 합성기 설계가 더 복잡해집니다. 주파수 변환 기반 회로에 내재된 또 다른 문제는 잘못된 주파수 잠금입니다(예: 믹서 미러 채널을 사용할 때). 이를 위해서는 예를 들어 디지털-아날로그 변환기(DAC)를 사용하여 VCO 주파수를 상당히 정확하게 사전 조정해야 합니다. 이는 결국 작동 온도 범위에 걸쳐 VCO의 주파수 튜닝 특성에 대해 극도로 높은 선형성(및 반복성)을 요구할 뿐만 아니라 온도 드리프트를 보상하기 위해 이 특성을 정확하게 교정해야 합니다. 또한 디지털-아날로그 변환기는 일반적으로 잡음 수준이 높기 때문에 합성기의 잡음 특성에 직접적인 영향을 미치며 필요한 주파수로 사전 튜닝한 후 DAC를 PLL 루프에서 제거해야 합니다.

총 분할 계수를 줄이는 또 다른 방법은 분수 분할 계수를 사용하는 것입니다. 이는 빈도를 다음과 같이 나누어 달성됩니다. N+1 모든 중신호의 기간과 나누기 N남은 시간 동안. 이 경우 평균 분할 계수는 다음과 같습니다. (N+1)/ 중, 어디 N그리고 중- 정수. 주어진 주파수 단계 크기에 대해 분수 분할 회로를 사용하면 위상 검출기의 입력에서 더 높은 비교 주파수를 사용할 수 있으므로 위상 잡음이 감소하고 합성기의 튜닝 속도가 증가합니다. 분수 분할 기술의 주요 단점은 분수 분할 메커니즘에 내재된 위상 오류로 인해 비고조파 스펙트럼 성분의 함량이 증가한다는 것입니다.

매우 효과적인 해결책은 위에서 설명한 디지털 신디사이저를 사용하는 것입니다( DDS), 이는 본질적으로 분수 주파수 분배기이기도 합니다. 디지털 신디사이저는 그림 1에 표시된 것처럼 기준 신호 소스 또는 분수 주파수 분배기로 사용할 수 있습니다. 각각 10, 11. PLL 루프에 주파수 분배기가 있기 때문에 20dB/옥타브까지 저하되는 디지털 신시사이저 출력 신호의 스펙트럼 구성에 특별한 주의를 기울여야 합니다. 이러한 관점에서 볼 때, 그림 1의 구성은 다음과 같다. 10은 위에서 논의한 혼합 단계를 도입할 수 있기 때문에 더 유연해 보입니다. 그림에 표시된 다이어그램에도 불구하고. 11과 같으며 주파수 분배기가 포함되어 있지 않지만 디지털 신시사이저의 입력(클럭) 주파수와 출력 주파수의 비율에 따라 동일한 정도의 열화 현상이 발생합니다.

|

|

디지털 신시사이저의 스펙트럼 특성을 개선하기 위해 위에서 설명한 방법은 매우 높은 필터링 특성을 갖는 PLL 회로에서 효과적으로 작동한다는 점에 유의해야 합니다. 그리고 디지털 신디사이저를 사용하면 회로가 다소 복잡해지기는 하지만 그럼에도 불구하고 전체적인 디자인은 기술적으로나 비용적으로 좋은 특성을 가질 것으로 보입니다.

VCO 선택

PLL 합성기의 설계는 주로 사용되는 VCO의 매개변수에 따라 결정됩니다. 역사적으로 신디사이저 개발자는 주로 생성된 주파수 범위가 넓고 위상 잡음이 낮은 것이 특징인 YIG 발진기에 의존해 왔습니다. 또한 YIG 발진기는 선형(및 반복 가능) 튜닝 특성을 나타내므로 다중 루프 PLL 시스템에서 초기 튜닝 및 주파수 잠금이 더 쉬워집니다. YIG 오실레이터의 이러한 독특한 특징은 오랫동안 이를 기반으로 한 신디사이저의 지배력을 보장해 왔습니다.

그러나 모든 YIG 발전기에 내재된 높은 에너지 소비, 크기, 높은 비용, 특히 낮은 튜닝 속도로 인해 반도체 발전기로의 전환이 미리 결정되었습니다. 현재 고주파(최대 10GHz 이상) 고체 조정 가능 발진기는 저렴한 집적 회로 형태로 제공됩니다. 이러한 오실레이터의 잡음 특성은 YIG 오실레이터에 비해 상당히 나쁘기 때문에 합성기 설계자는 주로 기준 신호 소스의 잡음 특성에 의존해야 합니다. 현재 상용 수정 발진기는 20~100kHz 오프셋, 100MHz 주파수에서 -160~176dBc/Hz 범위의 위상 잡음을 나타냅니다. 이 값은 10GHz 및 동일한 디튜닝 주파수로 변환할 때 -120...-136dBc/Hz에 해당하며, 이는 YIG 발생기의 잡음 특성과 비슷하고 심지어 더 우수합니다. 물론, 합성기의 개별 소자의 잡음 특성은 기준 신호를 변환하는 과정에서 눈에 띄는 영향을 미치지 않는다고 가정한다. 이 가정에는 약간의 창의적인 엔지니어링이 필요하지만 최종 결과는 분명합니다. 반도체 발진기를 기반으로 하는 합성기는 비싸고 부피가 크며 전력을 많이 소모하는 YIG 발진기를 사용하지 않고도 뛰어난 잡음 및 스펙트럼 성능과 함께 매우 높은 튜닝 속도를 잠재적으로 달성할 수 있습니다.

향후 개발

아날로그 신디사이저는 오늘날 가장 발전된 아키텍처로, 매우 높은 튜닝 속도와 낮은 위상 노이즈를 제공합니다. 비용 특성이 일반적인 비용 절감 추세와 일치하지 않더라도 아날로그 신디사이저는 저렴한 비용이 주요 요소가 아닌 일부 응용 분야에서 탁월한 솔루션이 될 수 있습니다. 디지털 신디사이저의 동작 주파수가 증가함에 따라 일부 비용 절감이 예상되며, 이는 아날로그 신디사이저 설계를 단순화할 수 있습니다.

디지털 신시사이저는 GaAs, Si 및 SiGe 기술의 급속한 발전으로 인해 엄청난 잠재력을 갖고 있습니다. 디지털 신디사이저의 동작 주파수와 스펙트럼 특성이 높아져 아날로그 및 PLL 신시사이저 설계에 큰 도움이 될 것으로 기대된다.

그러나 가까운 미래에 가장 유망한 개발은 저렴한 발진기 집적 회로를 기반으로 한 PLL 합성기와 관련이 있을 것으로 보입니다. 주요 노력은 합성기의 개별 요소의 고유 잡음을 줄여 PLL 필터의 최적 대역폭을 수 MHz로 확장하는 데 목표를 두고 있습니다. 여기서 고체 발진기는 잡음 특성에서 YIG 발진기와 경쟁하게 됩니다. 이를 통해 YIG 발생기 고유의 소음 수준을 유지하면서 마이크로초 범위의 주파수 튜닝 속도를 달성할 수 있습니다. PLL 합성기에 내재된 저렴한 비용과 함께 이러한 특성은 향후 설계에서 PLL 합성기의 지배력을 미리 결정하게 될 것입니다.

문학:

- J. Browne, "주파수 합성기 Tune Communications Systems", Microwaves&RF, 2006년 3월.

- V. Kroupa, "주파수 합성 이론, 설계 및 응용" 뉴욕: Willey, 1973.

- V. Manassewitsch, “주파수 합성기 이론 및 설계,” 제3판, 뉴욕: John Wiley & Sons, 1987.

- U. Rohde, “마이크로파 및 무선 합성기: 이론 및 설계” 뉴욕: John Wiley & Sons, 1997.

- J. Klapper 및 J. Frankle, "위상 고정 및 주파수 피드백 시스템", 뉴욕: Wiley, 1972.

- "24GHz 네트워크 분석기", Rohde & Schwartz 작성, Microwave Journal, 2005년 10월.

- Z. Galani 및 R. Campbell, "레이더용 주파수 합성기 개요", IEEE Transactionson 마이크로파 이론 및 기술, vol. MTT-39, 1991, pp. 782-789.

- V. Kroupa, “직접 디지털 주파수 합성기” 뉴욕: IEEE Press, 1999.

- T. Endres, R. Hall 및 A. Lopez, IEEE 국제 주파수 제어 심포지엄 Proc., 1994년, "군용 우주 응용 분야를 위한 DDS 기반 합성기의 설계 및 분석 방법", pp. 625-632.

- W. Egan, “위상 잠금에 의한 주파수 합성” 뉴욕: Wiley, 2000.

- R. Best, "위상 고정 루프 - 이론, 설계 및 응용" 뉴욕: McGraw-Hill, 1984.

- U. Rohde, “디지털 PLL 합성기: 설계 및 애플리케이션” NJ: Prentice Hall, 1983.

- A. 블랜차드, “위상 고정 루프” 뉴욕: Wiley, 1976.

- F. Gardner, "Phaselock Techniques" 제2판, 뉴욕: Wiley, 1979.

- "Fractional-N Synthesizer" 애플리케이션 노트, Synergy Microwave Corporation, http://www.synergymwave.com/> www.synergymwave.com.

- Valpey Fisher Corporation의 "고주파 기준 모듈", Microwave Journal, 2005년 4월.

작가에 대해

Alexander Chenakin은 기술 과학 후보인 Kiev Polytechnic Institute를 졸업했습니다. 그는 다양한 엔지니어링 및 관리직에서 근무했으며 마이크로파 신호 발생 분야의 첨단 기술을 연구하는 컨설팅 회사를 이끌었습니다. 그는 현재 미국 새너제이의 Phase Matrix에서 주파수 합성 부서의 이사로 재직하면서 다양한 측정 기기 및 시스템을 위한 차세대 주파수 합성기 개발을 감독하고 있습니다.

우리는 최고의 제조업체의 제품을 제공합니다

PRIST는 측정 문제에 대한 최적의 솔루션을 제공합니다.

당사에서는 오실로스코프, 전원 공급 장치, 신호 발생기, 스펙트럼 분석기, 교정기, 멀티미터, 전류 클램프를 구입할 수 있을 뿐만 아니라 측정 장비를 확인하거나 교정할 수도 있습니다. 우리는 세계 최대의 측정 장비 제조업체와 직접 계약을 맺고 있으며, 이를 통해 귀하의 문제를 해결할 장비를 선택할 수 있습니다. 풍부한 경험을 바탕으로 다음 브랜드의 제품을 추천해 드릴 수 있습니다.

트랜시버 장치의 주파수 안정성 문제는 항상 존재해 왔습니다. 상대적으로 낮은 주파수(최대 100-150MHz)에서는 석영 공진기를 사용하여 해결되었으며, 더 높은 주파수(400MHz)에서는 표면 탄성파(SAW 공진기) 기반 공진기를 사용하여 해결되었습니다. 고품질의 재료가 자주 사용됩니다.세라믹 또는 기타 높은 Q 공진기. 수동 구성 요소를 사용하여 설명된 안정화 방법은 단순성과 비교적 낮은 구현 비용이라는 장점이 있지만 주요 단점은 주파수 설정 요소인 공진기를 변경하지 않고는 중요한 주파수 튜닝이 불가능하다는 것입니다. 안정성을 유지하면서 작동 주파수를 전자적으로 신속하게 조정할 수 없기 때문에 무선 장치의 사용이 크게 제한되며, 예를 들어 다중 채널 구현이 허용되지 않습니다.

현재 널리 사용되고 있는 다양한 외국 기업의 통합 주파수 합성기는 높은 안정성을 유지하면서 초고주파를 포함한 작동 주파수의 신속한 전자 튜닝이 가능합니다. 이러한 주파수 합성기는 직접 유형과 간접 유형이 있습니다. 직접 합성의 장점은 작은 주파수 그리드 단계에서 높은 성능을 갖는다는 점이지만, 수많은 비선형 신호 변환으로 인해 발생하는 많은 수의 스펙트럼 성분을 필터링해야 하기 때문에 직접 합성 장치는 마이크로파 회로에 거의 사용되지 않습니다. 초고주파를 합성하려면 일반적으로 간접 합성기 또는 PLL(위상 고정 루프) 합성기가 사용됩니다. PLL이 있는 통합 신시사이저에는 두 가지 주요 유형이 있습니다. 프로그래밍 가능(주파수 값이 3선 버스를 통해 외부 마이크로컨트롤러에 의해 설정됨)과 비 프로그래밍 가능(내부 주파수 분배기의 분배 계수가 고정됨) 기준 주파수는 외부 석영 공진기에 의해 설정됩니다. 간단한 마이크로파 회로에서는 일반적으로 프로그래밍이 불가능한 통합 합성기가 사용됩니다(예: Motorola의 MC12179). 단점은 항상 가능한 것은 아닌 석영 공진기를 정확하게 선택해야 한다는 점입니다. Philips의 UMA1020M과 같은 프로그래밍 가능 주파수 합성기는 이러한 단점이 없으며 최신 통신 시스템에는 항상 제어 마이크로컨트롤러가 있으므로 이러한 합성기를 프로그래밍하는 것은 기술적으로 쉽습니다. 초고주파 범위의 자동 발전기는 하이브리드 기술을 사용하여 제작된 기능적으로 완전한 모듈 형태로 사용됩니다.

설명된 솔루션을 적용한 예는 이 기사에서 제안된 간단한 실험실 초고주파 합성기입니다. 이를 통해 1900~2275MHz 범위의 주파수를 높은 정확도로 생성하고 안정화할 수 있습니다.

설계된 합성기의 블록 다이어그램은 그림 1에 나와 있습니다. 1. 외관 - 그림 2. 회로를 볼 수 있듯이 합성기는 Mini-Circuits JTOS-2200의 전압 제어 발진기(VCO 또는 VCO) JTOS-2200, 통합 주파수 합성기 UMA-1020M 및 Zilog의 마이크로 컨트롤러 Z86E0208PSC로 구성됩니다.

VCO에 의해 생성된 마이크로파 신호는 실험실 합성기의 출력과 UMA-1020M 회로에 포함된 주요 프로그래밍 가능 주파수 분배기의 입력에 공급됩니다.

JCO-8 수정 발진기에 의해 생성된 기준 신호는 UMA-1020M 회로에도 포함되어 있는 프로그래밍 가능한 보조 주파수 분배기에 공급됩니다. UMA-1020M의 블록 다이어그램은 그림 1에 나와 있습니다. 3, UMA-1020M에 대한 자세한 기술 문서는 제조업체 웹사이트(http://www.philips.de/)에서 확인할 수 있습니다. 두 분배기(메인 및 보조)의 계수는 3선(데이터 데이터, CLK 동기화 및 쓰기 권한/활성화) 버스를 통해 Z86E0208PSC 마이크로컨트롤러에 의해 설정됩니다. Z86E0208PSC 마이크로 컨트롤러의 블록 다이어그램은 그림 1에 나와 있습니다. 4. 마이크로컨트롤러의 내부 ROM은 7개의 서로 다른 주파수 값과 1개의 테스트 모드를 프로그래밍하는 데 충분합니다. 특정 주파수 값(또는 테스트 모드)은 실험실 합성기의 인쇄 회로 기판에 있는 점퍼로 설정됩니다. 다음 주파수 값을 통합 신디사이저에 로드하기 전에 마이크로 컨트롤러는 점퍼에 연결된 포트를 폴링하고 수신된 데이터에 따라 하나 또는 다른 펌웨어를 선택합니다. 신디사이저 보드의 전원을 켜면 새로운 주파수 값이 자동으로 설정됩니다. Z86E0208PSC 마이크로컨트롤러의 합성기 프로그래밍 알고리즘은 그림 1에 나와 있습니다. 5, 프로그램 목록이 제공됩니다.

Zilog 마이크로컨트롤러 프로그래밍에 대한 자세한 내용은 웹사이트 http://www.zilog.com/에서 확인할 수 있으며, 전체 기술 문서는 웹사이트에서 확인할 수 있습니다.

사용된 JTOS-2200 VCO의 특별한 특징은 튜닝 전압 범위(0.5~5V)입니다. 즉, 설정전압 값이 0.5V 미만일 경우 제조사에서는 안정적인 발진 발생을 보장하지 않습니다. 수행된 실험은 이 진술의 진실성을 보여주었습니다.

PLL의 작동 원리와 피드백 필터(루프 필터)를 계산하는 방법은 기술 문헌에서 상당히 광범위하고 반복적으로 논의되므로 이 기사에서는 논의하지 않습니다. 피드백 필터 매개변수를 계산할 수 있는 무료 프로그램이 여러 개 있으며 인터넷 http://www.analog.com/ 또는 www.national.com에서 찾을 수 있습니다.

합성기 회로의 올바른 작동을 모니터링하기 위해 LED가 보드에 설치되며, LED의 빛은 주파수 합성 오류를 나타냅니다. 신디사이저가 제대로 작동하면 LED가 켜지지 않아야 하지만 이 기능은 소프트웨어로 비활성화할 수 있습니다.

조립된 실험실 합성기의 비용은 $30를 초과하지 않습니다. 제안된 장치의 비용을 줄이기 위해 두 가지 방법을 제안할 수 있습니다. 첫째, Z86E0208PSC의 최대 클록 주파수가 8MHz인 반면 UMA의 경우 합성기의 석영 기준 발진 소스와 마이크로 컨트롤러를 결합할 수 있습니다. -1020M은 5~40MHz 이내일 수 있습니다. 둘째, VCO는 주어진 방법론을 사용하여 트랜지스터 또는 증폭 집적 회로를 사용하여 독립적으로 개발될 수 있습니다.

사용된 문헌 목록

- 유전체 공진기 / M.E. 일첸코, V.F. Vzyatyshev, L.G. Gassanovet al.; 에드. 나. 일첸코. – M.: 라디오 및 통신, 1989. – 328 p.: 아픈. – ISBN 5-256-00217-1.

- Pestryakov A.V. 합성 및 주파수 안정화 장치용 집적 회로 // Chip News. – 1996. - 2호.

- Lobov V., Steshenko V., Shakhtarin B. 직접 주파수 합성을 위한 디지털 신디사이저 // Chip News. – 1997. - 1위.

- 무선 반도체 솔루션. 모토로라. 디바이스 데이터 - Vol.1. DL 110/D, 개정판 9.

- VCO 디자이너 핸드북 2001. VCO/HB-01. 미니 회로.

- 글래드스타인 M.A. Zilog의 Z86 제품군 마이크로컨트롤러. 프로그래머 가이드. -M .: DODEKA, 1999, 96p.

- Z8 애플리케이션 노트 핸드북. Zilog. DB97Z8X0101.

- Starikov O. PLL 방법 및 고주파 신호 합성 원리//Chip News. – 2001. - 6호.

- 마이크로파 발진기 설계. 애플리케이션 노트 A008// Hewlett-Packard Co. - 발행번호 5968-3628E(6/99)

- Shveshkeyev P. 2.4~2.5GHz ISM 대역//응용 마이크로파 및 무선의 WLAN 애플리케이션을 위한 VCO 설계. – 2000. - 6번. – P.100-115.

마이크로파 장치를 개발하고 설정할 때 라디오 아마추어는 필요한 주파수 범위에서 측정 장비가 부족하여 종종 어려움을 겪습니다. 제안된 주파수 합성기는 아마추어 조건에서 제작될 수 있다. 1900~2275MHz 범위에서 작동합니다. 주파수 값은 스위치를 사용하여 여러 가지 가능한 값 중에서 선택됩니다.

상대적으로 낮은 주파수(최대 100~150MHz)에서 발생기의 주파수를 안정화하는 문제는 석영 공진기를 사용하여 해결되며, 더 높은 주파수(400MHz)에서는 표면 탄성파(SAW 공진기)의 공진기를 사용하여 해결됩니다. 마이크로파 주파수에서는 고품질 세라믹의 유전체 공진기와 기타 고품질 공진기를 사용합니다. 수동 구성 요소를 사용한 안정화에는 단순성과 상대적으로 낮은 구현 비용이라는 장점이 있습니다. 가장 큰 단점은 주파수 설정 요소를 변경하지 않고 생성된 신호의 주파수를 크게 변경할 수 없다는 것입니다.

널리 보급된 통합 주파수 합성기를 사용하면 고주파 안정성을 유지하면서 발전기(마이크로파 포함)의 빠른 전자 튜닝을 구현할 수 있습니다. 신디사이저에는 직접형과 간접형이 있습니다.

직접 합성의 장점은 빠른 주파수 변경 속도와 작은 단계의 튜닝으로 간주됩니다. 그러나 수많은 비선형 변환으로 인해 합성된 신호에 다수의 스펙트럼 성분이 존재하기 때문에 직접 합성 장치는 마이크로파 장비에 거의 사용되지 않습니다.

마이크로파 합성의 경우 위상 고정 루프(PLL)가 있는 간접 합성기가 사용되는 경우가 많습니다. PLL의 작동 원리와 피드백 필터 계산 방법은 다음과 같은 문헌에서 광범위하고 반복적으로 논의되었습니다. 피드백 필터의 최적 매개변수를 계산할 수 있는 무료 배포 프로그램이 여러 개 있으며 인터넷에서 찾을 수 있습니다.

PLL이 포함된 통합 합성기는 프로그래밍 가능(주파수 값이 외부 명령에 의해 설정됨)과 프로그래밍 불가능(기준 주파수의 고정 곱셈 및 나눗셈 계수를 변경할 수 없음)의 두 가지 유형이 있습니다.

예를 들어 MC12179와 같이 프로그래밍이 불가능한 통합 신디사이저의 단점은 정확하게 지정된 주파수의 석영 공진기를 사용해야 한다는 점이며, 이는 항상 가능하지는 않습니다. UMA1020M과 같은 프로그래밍 가능 신디사이저에는 이러한 단점이 없습니다. 제어 마이크로컨트롤러가 있는 경우 이러한 신디사이저를 특정 주파수로 설정하는 것은 기술적으로 쉽습니다. 합성기 마이크로 회로와의 협력에 필요한 전자 주파수 튜닝 기능을 갖춘 마이크로파 자체 발진기는 하이브리드 기술을 사용하여 제작된 기능적으로 완전한 모듈 형태로 소비자에게 제공됩니다.

2GHz 범위의 장비 설정을 확인하고 조정하기 위한 실험실 주파수 합성기의 다이어그램이 그림 1에 나와 있습니다. 그 기반은 UMA-1020M(DA3) 마이크로 회로이며 기술 문서는 다음에서 찾을 수 있습니다. 제조업체의 웹 사이트

또한 합성기에는 전압 제어 발진기(VCO) DA1, 10MHz 수정 발진기 DA2 및 마이크로컨트롤러 DD1이 포함되어 있습니다. VCO 출력의 마이크로파 신호는 합성기(커넥터 XW1)의 출력과 DA3 칩의 프로그래밍 가능한 기본 주파수 분배기의 입력으로 이동합니다. DA2 생성기 출력의 기준 주파수 신호는 DA3 마이크로 회로의 일부이기도 한 프로그래밍 가능한 보조 주파수 분배기에 공급됩니다.

메인 및 보조 분배기의 주파수 분배 계수는 마이크로컨트롤러 DD1(Z86E0208PSC)에 의해 설정되며 3선 정보 버스(핀 11-13 DA3)를 통해 해당 명령을 보냅니다. 제어 프로그램의 소스 텍스트는 표에 나와 있습니다. 1. 마이크로컨트롤러의 내부 메모리는 7개의 서로 다른 주파수 값에 대한 데이터를 저장하기에 충분합니다. 주파수 값 중 하나 또는 출력에 신호가 없는 모드는 표에 따라 점퍼 S1-S3을 사용하여 선택됩니다. 2. 설정 모드는 장치를 켜는 순간부터 적용되며, 이후에는 장치를 다시 켤 때까지 스위치를 조작해도 작동에 영향을 미치지 않습니다. HL1 LED는 전원을 켠 후 1초 후에 꺼져야 합니다. Zilog 마이크로컨트롤러 프로그래밍에 대해 읽을 수 있습니다.

합성기는 인쇄 회로 기판에 조립되며 그 모양은 그림 1에 나와 있습니다. 2. 표면 실장 저항기와 커패시터가 사용됩니다.

문학

- Starikov O. PLL 방법 및 고주파 신호 합성 원리. - 칩 뉴스, 2001, No. 6.

- VCO 디자이너 핸드북 2001. VCO/HB-01. - 미니 회로.

- Zilog의 Z86 제품군 Glvdshtein M.A. 마이크로컨트롤러. 프로그래머 가이드. -M .: DODEKA, 1999, 96p.

마이크로파 합성기 외에도 UMA1020M 칩에는 20..300MHz의 주파수 범위에서 작동하는 또 다른 칩이 포함되어 있습니다. 6n은 설명된 설계에 사용되지 않습니다.